## **Document Name**

# Failure Analysis Final Report

27199

ERMA#

| Bruce Wu                                      | Date Received              |

|-----------------------------------------------|----------------------------|

| QA Department                                 | Date of Report             |

| Flextronics Manufacture Zhuhai                | Referring Apps Engine      |

| Xin Qing Science & Industrial Park , Jing An, | Distributor                |

| 519000, Doumen , Zhuhai , P. R. China.        | <b>Evaluating Engineer</b> |

| Date Received           | 11 <sup>th</sup> March 2019 |  |

|-------------------------|-----------------------------|--|

| Date of Report          | 10 <sup>th</sup> April 2019 |  |

| Referring Apps Engineer | Zawani Mohamad Yusof        |  |

| Distributor             | N/A                         |  |

| Evaluating Engineer     | Alia Nabila Ismail          |  |

#### **Contacts**

| Zawani Mohamad Yusof | Field:     |

|----------------------|------------|

|                      | Corporate: |

#### **Device List (Legacy Products)**

| # | Device          | Lot Number | Top Datecode | Top ID/ Bottom Mark | Failure |

|---|-----------------|------------|--------------|---------------------|---------|

| 1 | EP4CGX75DF27C7N | S902AF66   | G CAAAF1901E | 3N1GE9A0D           | 1       |

| 2 | EP4CGX75DF27C7N | S849MKB7   | G BAAAF1901E | 3N9GE8Y0O           | 6       |

| 3 | EP4CGX75DF27C7N | S902AF66   | G CAAAF1901E | 3N1GE9A0D           | 6       |

#### **Failure Mechanism Codes**

| 1 | No Trouble Found        | 5 | Test Coverage | 9  | Unknown Cause    | 13 | Corrupted       |

|---|-------------------------|---|---------------|----|------------------|----|-----------------|

|   |                         |   |               |    |                  |    | Imprint         |

| 2 | Electrical Overstress   | 6 | Fabrication   | 10 | Component Design | 14 | Untestable      |

|   |                         |   | Defect        |    |                  |    |                 |

| 3 | Electrostatic Discharge | 7 | Delamination  | 11 | Package          | 15 | Other (Specify) |

| 4 | Retention               | 8 | Programmer    | 12 | Factory Error    | 16 | Control Unit    |

#### **History of Failure**

# Reported Failure:

End Customer: CISCO

Customer found 1pce Dagger failed at 2C test with failure code "GET\_ROMMON", and based on the failure symptom as failed log shows and debug preliminary analysis( eliminated process issue after visually inspected and 2D/5D X-ray test), the failure was related with U1\_F1(FPGA), after they did A-B-A swap test, it is true component issue

Failure Rate: 0.286% (1 Out of 350 Devices)

Where Failure Occurred: [] Programming [] Board Assembly [] Board Inspection [X] Board Test

[] End User Inspection [] Field After ( ) Months [] Unknown [] Other (specify)

Other Relevant Information: N/A

Report Template 11G-00503C Rev02 Intel Confidential Page 1 of 4

To the extent information in this document is provided in connection with Intel products, no license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document, except as provided by Intel's or its subsidiaries' terms and conditions of sale for such products. Intel assumes no liability and disclaims any express or implied warranty regarding the information in the document, including any liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. If this product is used by our customer for any application where personal injury or death may occur, the customer is responsible for properly qualifying the product for that application. Any recommended operating methods are correct to Intel's reasonable knowledge at the time of writing. Intel accepts no liability for the implementation of these methods within the customer's manufacturing environment. All plan dates specified are target dates and are subject to change. Intel, Altera, Enpirion, the Intel/Altera/Enpirion logos, and Intel/Altera/Enpirion product names, are trademarks of Intel Corporation in the U.S. and other countries. Other names and brands may be claimed as the property of others.

| Document Name                 | ERMA# |  |

|-------------------------------|-------|--|

| Failure Analysis Final Report | 27199 |  |

**Analysis Methods Performed**

| Non-Invasive:                |                    | Invasive:         |                    |

|------------------------------|--------------------|-------------------|--------------------|

| [ <b>X</b> ] External Visual | [] Design Review   | [] Decap Package  | [] Delayering      |

| [] X-Ray                     | [] Verify on Bench | [] IR Microscopy  | [] Cross Section   |

| [X] C-SAM                    |                    | [] Liquid Crystal | [] FIB             |

| [X] Production Test          |                    | [] EMMI / OBIRCH  | []SEM              |

| [] IV Curve                  |                    | [] Microprobing   | []EDX              |

| []TDR                        |                    |                   | [] Other (Specify) |

|                              |                    |                   |                    |

## **Test Results (FPGA)**

| # | Opens | Shorts | Icc Standby | RAM  | Functional | Comments                                    |

|---|-------|--------|-------------|------|------------|---------------------------------------------|

| 1 | Pass  | Pass   | Pass        | Pass | Pass       | No trouble found                            |

| 2 | Pass  | Pass   | Pass        | Pass | Failed     | Unit failed functional test at 0°C and 25°C |

| 3 | Pass  | Pass   | Pass        | Pass | Failed     | Unit failed functional test at 0°C          |

## **Analysis Procedures and Results**

Upon receiving, the marking on the returned devices were verified to be consistent against the Device Problem Report.

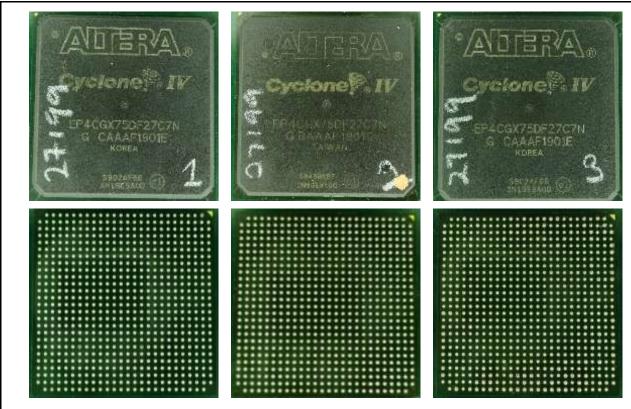

At visual inspection, the solder balls of the devices were found to be deformed as expected after device extraction from customer's board (Figure 1).

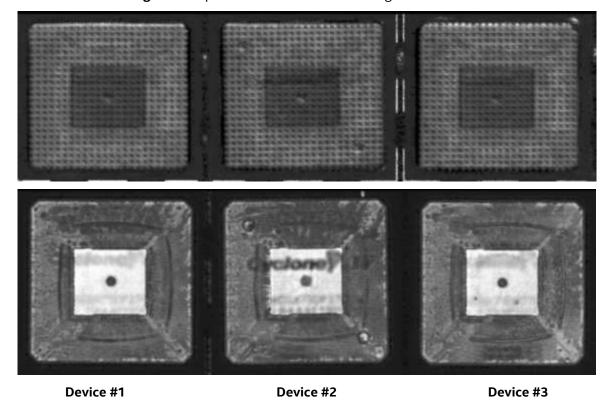

C-SAM inspection was performed on the returned devices and no anomaly were observed. (Figure 2)

After being baked to remove excess moisture, the devices were reworked with new solder balls.

All devices were then tested with Production Final Test Flow that tests for DC parametric and device functionality.

#### Device #1:

The device passed all test across all temperatures of 0°C, 25°C and 85°C. No failing behavior was observed on the device.

#### **Device #2 and #3:**

Device #2 and #3 failed functional tests at low temperatures. Additional characterization showed:

- Device#2 failed transceiver output buffer test and transceiver ICDR (Interpolator Clock Data Recovery) speed test at 25°C and 0°C.

- Device#3 failed transceiver output buffer test and transceiver ICDR (Interpolator Clock Data Recovery) speed test at 0°C only.

ICC values of both ERMA devices are comparable to factory standard device, this rules out an electrical overstress damage (EOS) as cause of functional failures.

The devices failure was believed to be caused by a random defect. Such a defect is introduced into the devices during the wafer fabrication process, and can cause a latent failure. This kind of fabrication defect is random in nature, and does not pose any concern for reliability of other devices.

Report Template 11G-00503C Rev02 Intel Confidential Page 2 of 4

# **Document Name**

ERMA#

Failure Analysis Final Report

27199

# **Attached Pages**

Figure 1: Top and bottom view of incoming ERMA devices.

| Document Name                 | ERMA# |

|-------------------------------|-------|

| Failure Analysis Final Report | 27199 |

Figure 2: C-SAM inspection on incoming ERMA devices.

#### **Estimated Failure Rate of Problem**

The Cyclone IV GX device was manufactured in a 65 nm process technology. The Reliability Monitor Life Test results demonstrate a combined failure rate of 10. One FIT is equivalent to one failure in one billion device-hours.

## Plan for Reducing Incidence of Problem

Reliability monitors are performed on a regular basis in order to assure that normal production testing and process control methodologies produce reliable products. Intel PSG also has an on-going defect reduction program to improve yield and the quality of outgoing parts.

Report Template 11G-00503C Rev02 Intel Confidential Page 4 of 4