# NIOS II Hello WORLD

# QUARTUS 18.1

Nikki 01.08.2019

Question:

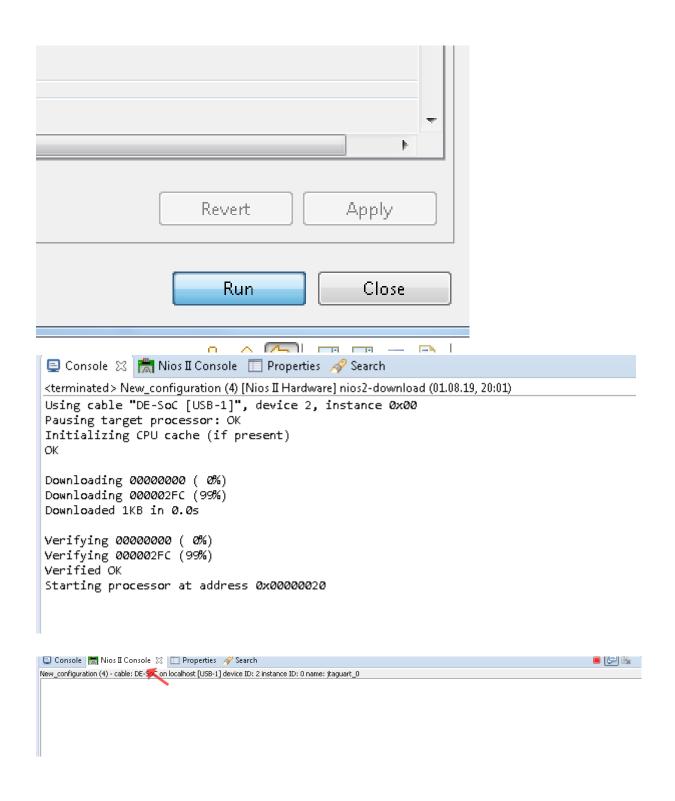

Why doesnt the NIOS II Console show Hello World!

( Also see Attachment)

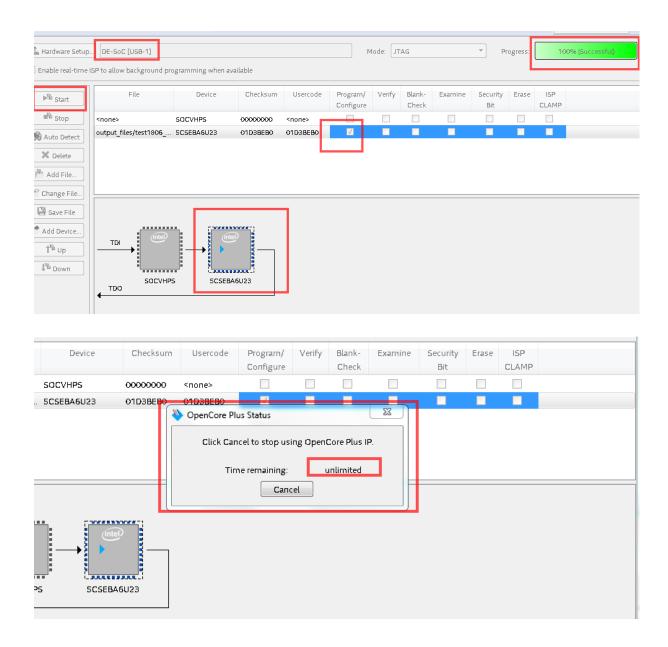

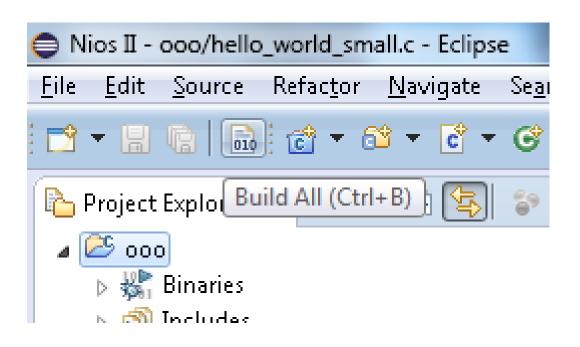

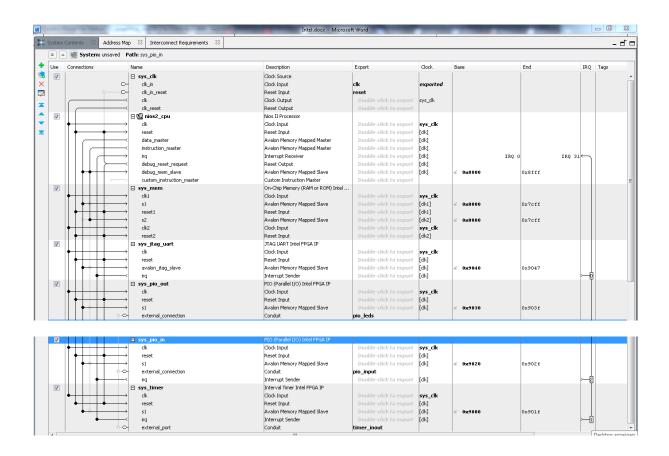

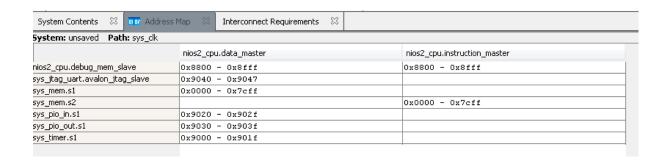

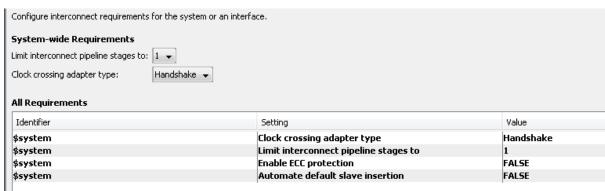

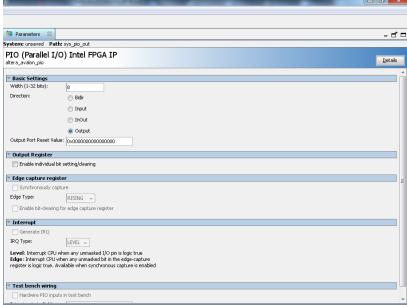

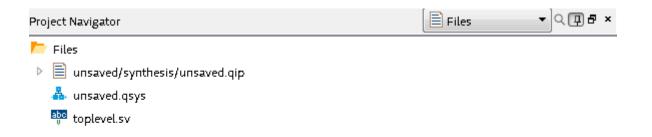

FIGURE 1 IPS

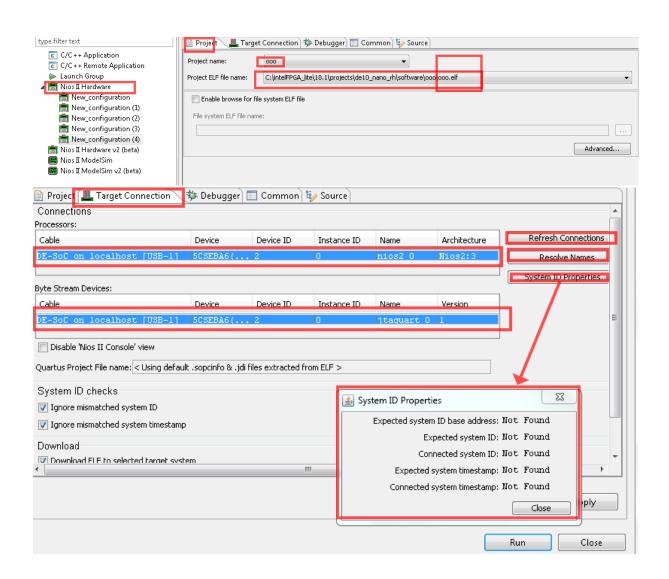

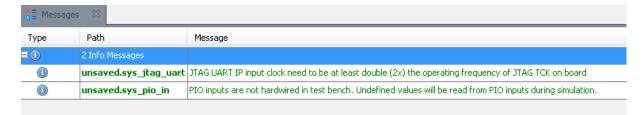

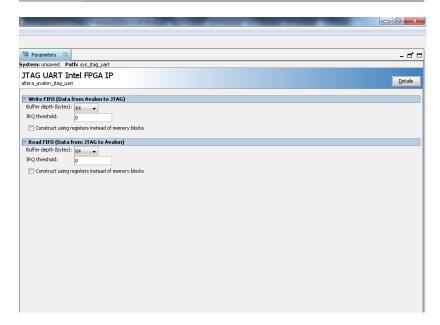

FIGURE 2 IPS

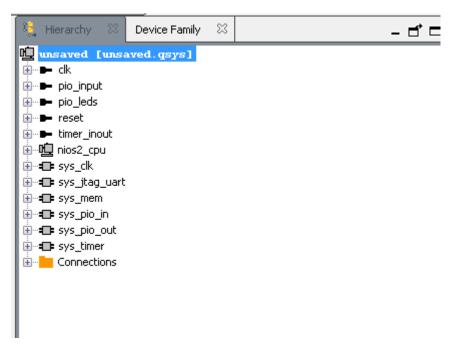

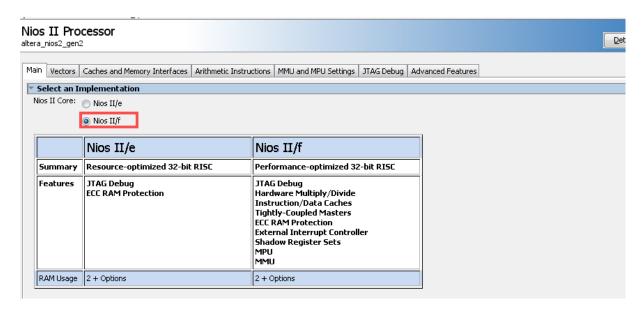

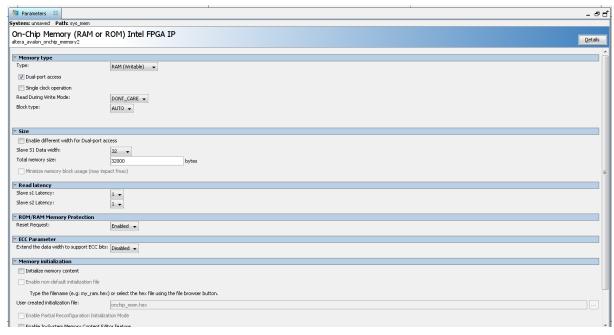

#### Nios II Processor altera\_nios2\_gen2 Main Vectors Caches and Memory Interfaces Arithmetic Instructions MMU and MPU Settings JTAG Debug Advanced Features Reset Vector Reset vector memory: sys\_mem.s2 Reset vector offset: 0x00000000 Reset vector: 0×00000000 Exception Vector Exception vector memory: sys\_mem.s2 Exception vector offset: 0×00000020 Exception vector: 0x00000020 ▼ Fast TLB Miss Exception Vector Fast TLB Miss Exception vector memory: None Fast TLB Miss Exception vector offset: 0x00000000 Fast TLB Miss Exception vector: 0x00000000

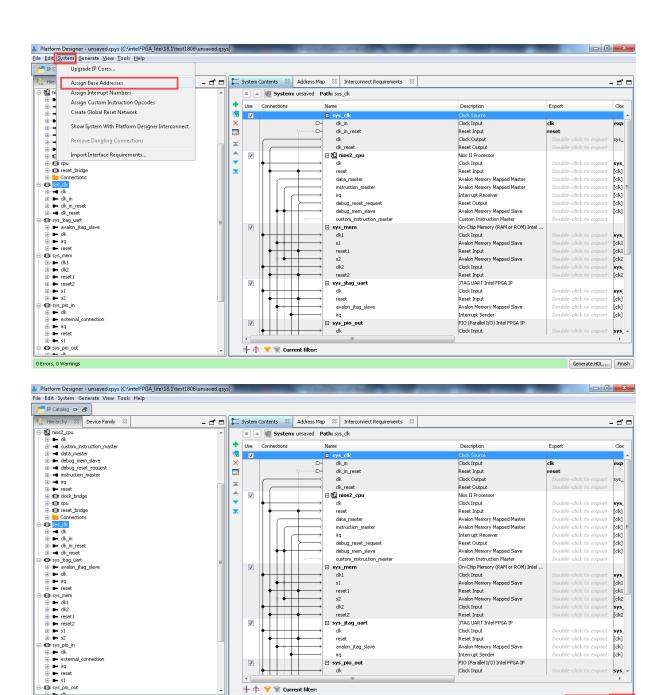

= sys\_pio\_out

V

0 Errors, 0 Warnings

🕂 🏚 😙 🗑 Current filter:

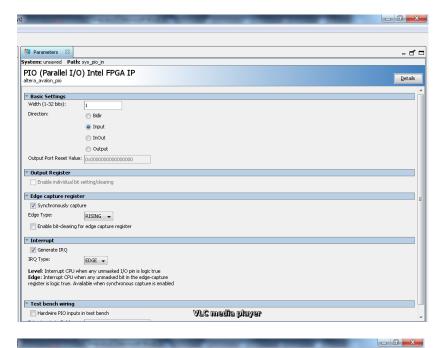

PIO (Parallel I/O) Intel FPGA IP Clock Input

Generate HDL... Finish

## **Toplevel**

Instanciate a NIOS II

```

// unsaved.v

// Generated using ACDS version 18.1 625

5

`timescale 1 ps / 1 ps

6

pmodule unsaved (

input wire

input wire

clk clk,

pio_input.export

8

pio_input_export, //

pio_leds.export

output wire [7:0] pio_leds_export, //

9

input wire

11

reset reset n,

reset.reset n

11

timer inout export // timer inout.export

output wire

);

13

14

wire [31:0] nios2_cpu_data_master_readdata;

// mm interc

wire

15

nios2_cpu_data_master_waitrequest;

// mm_interc

nios2 cpu data master debugaccess;

// nios2 cpu

wire [15:0] nios2 cpu data master address;

// nios2_cpu

17

wire [3:0] nios2_cpu_data_master_byteenable;

18

// nios2 cpu

19

wire

nios2_cpu_data_master_read;

// nios2_cpu

20

nios2_cpu_data_master_readdatavalid;

// mm_interc

wire

wire nios2_cpu_data_master_write;

// nios2_cpu

// nios2_cpu

wire [31:0] nios2_cpu_data_master_writedata;

```

### Warnings when compiling

Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM\_PARALLEL\_PROCESSORS in your QSF to an appropriate value for best performance.

Warning (12020): Port "jdo" on the entity instantiation of

"the\_unsaved\_nios2\_cpu\_cpu\_nios2\_oci\_itrace" is connected to a signal of width 38. The formal width of the signal in the module is 16. The extra bits will be ignored.

Warning (12188): Intel FPGA IP Evaluation Mode feature is turned on for the following cores Warning (12190): "Nios II Processor (6AF7\_00A2)" will use the Intel FPGA IP Evaluation Mode feature

Warning (12190): "Nios II Processor (6AF7 00A2)" will use the Intel FPGA IP Evaluation Mode feature

Warning (265072): Messages from megafunction that supports Intel FPGA IP Evaluation Mode feature

Warning (265073): Messages from megafunction that supports Intel FPGA IP Evaluation Mode feature Nios II Processor

Warning (265074): The reset input will be asserted when the evaluation time expires

Warning (265073): Messages from megafunction that supports Intel FPGA IP Evaluation Mode feature Nios II Processor

Warning (265074): The reset input will be asserted when the evaluation time expires

Warning (265074): The reset input will be asserted when the evaluation time expires

Warning (265069): Megafunction that supports Intel FPGA IP Evaluation Mode feature will stop functioning in 1 hour after device is programmed

Warning (12241): 3 hierarchies have connectivity warnings - see the Connectivity Checks report folder

Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM\_PARALLEL\_PROCESSORS in your QSF to an appropriate value for best performance.

Warning (292013): Feature LogicLock is only available with a valid subscription license. You can purchase a software subscription to gain full access to this feature.

Warning (15714): Some pins have incomplete I/O assignments. Refer to the I/O Assignment Warnings report for details

Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM\_PARALLEL\_PROCESSORS in your QSF to an appropriate value for best performance.

Warning (210042): Can't convert time-limited SOF into POF, HEX File, TTF, or RBF Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM\_PARALLEL\_PROCESSORS in your QSF to an appropriate value for best performance.