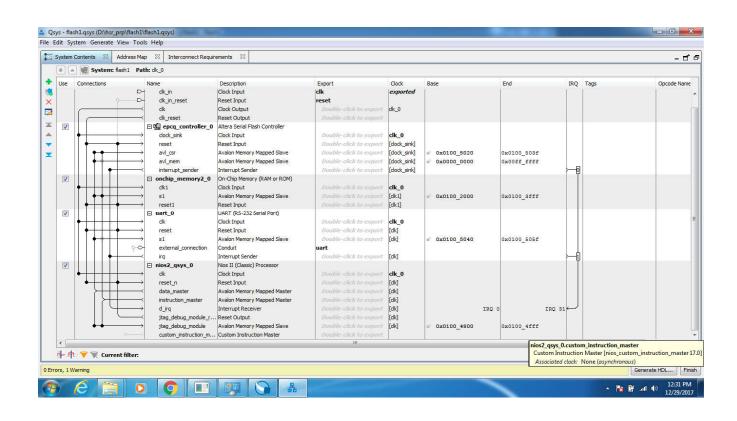

## 1. In QSYS I selected NIOS II (CLASSIC ) processor , UART, ON CHIP MEMORY, EPCQ CONTROLLER.

2. Base address are following

|          | cq_controller_0 |                             |                        |              |            |        |

|----------|-----------------|-----------------------------|------------------------|--------------|------------|--------|

|          | _sink           | Clock Input                 | Double-click to export | clk_0        |            |        |

| reset    | t               | Reset Input                 | Double-click to export | [clock_sink] |            |        |

| → avl_c  | csr             | Avalon Memory Mapped Slave  | Double-click to export | [clock_sink] | 0x0100_503 | f      |

| → avl_n  | mem             | Avalon Memory Mapped Slave  | Double-click to export | [clock_sink] | 0x00ff_fff | f      |

| < inter  | rupt_sender     | Interrupt Sender            | Double-click to export | [clock_sink] |            | -      |

| 🖃 onchi  | p_memory2_0     | On-Chip Memory (RAM or ROM) |                        |              |            |        |

| → clk1   |                 | Clock Input                 | Double-click to export | clk_0        |            |        |

| → s1     |                 | Avalon Memory Mapped Slave  | Double-click to export | [clk1]       | 0x0100_3ff | f      |

| reset    | t1              | Reset Input                 | Double-click to export | [clk1]       |            |        |

|          | -               |                             |                        | I            |            |        |

| nios2_c  | asys_0          | Nios II (Classic) Processor |                        |              |            |        |

| clk      |                 | Clock Input                 | Double-click to export | clk_0        |            |        |

| reset_r  | n I             | Reset Input                 | Double-click to export | [clk]        |            |        |

| data_m   | naster          | Avalon Memory Mapped Master | Double-click to export | [clk]        |            |        |

| instruct | tion_master     | Avalon Memory Mapped Master | Double-click to export | [clk]        |            |        |

| d_irq    |                 | Interrupt Receiver          | Double-click to export | [clk]        | IRQ 0      | IRQ 31 |

| jtag_de  | ebug_module_r   | Reset Output                | Double-click to export | [clk]        |            |        |

| jtag_de  | ebug_module     | Avalon Memory Mapped Slave  | Double-click to export | [dk]         | 0x0100_4ff | f      |

| custom   | _instruction_m  | Custom Instruction Master   | Double-click to export |              |            |        |

|          |                 |                             |                        |              |            |        |

Step2: IN reset vector memory I selected EPCQ CONTROLLER , in exception vector memory, I selected onchipmemory and reset vector and exception vector address taking automatically by default.

| * Reset Vector           |                             |       |  |  |

|--------------------------|-----------------------------|-------|--|--|

| Reset vector memory:     | epcq_controller_0.avl_csr + |       |  |  |

| Reset vector offset:     | 0x0000000                   |       |  |  |

| Reset vector:            | 0x01005020                  |       |  |  |

| Exception Vector         |                             |       |  |  |

| Exception vector memory: | onchip_memory2_0.s1         | · • ] |  |  |

| Exception vector offset: | 0x0000020                   |       |  |  |

| Exception vector:        | 0x01002020                  |       |  |  |

| ameters 🕄                                                     |                                                                     |                                                                                                 |                                                                                                                                                              |   |  |

|---------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|

| em: flash1 Path: nios2                                        |                                                                     |                                                                                                 |                                                                                                                                                              |   |  |

| s II (Classic) Pr                                             | ocessor                                                             |                                                                                                 |                                                                                                                                                              |   |  |

| 405 II Core:                                                  | <ul> <li>Nios II/e</li> <li>Nios II/s</li> <li>Nios II/f</li> </ul> |                                                                                                 |                                                                                                                                                              |   |  |

|                                                               | Nios II/e                                                           | Nios II/s                                                                                       | Nios II/f                                                                                                                                                    |   |  |

| Nios II<br>Selector Guide                                     | RISC<br>32-bit                                                      | RISC<br>32-bit<br>Instruction Cache<br>Branch Prediction<br>Hardware Milipiy<br>Hardware Divide | RISC<br>32-bit<br>Instruction Cache<br>Branch Prediction<br>Hardware Nultply<br>Hardware Divide<br>Barrel Shifter<br>Data Cache<br>Dynamic Branch Prediction |   |  |

| Memory Usage (e.g Strati                                      | ix IV) Two M9Ks (or equiv.)                                         | Two M9Ks + cache                                                                                | Three M9Ks + cache                                                                                                                                           |   |  |

| Hardware Arithmetic (                                         | Operation                                                           |                                                                                                 |                                                                                                                                                              | • |  |

| Hardware multiplication typ                                   |                                                                     | -                                                                                               |                                                                                                                                                              |   |  |

| Reset Vector                                                  |                                                                     | 1                                                                                               |                                                                                                                                                              |   |  |

| Reset vector memory:<br>Reset vector offset:<br>Reset vector: | epcq_controller_0,avl_<br>0x00000000<br>0x01005020                  | çar 🔻                                                                                           |                                                                                                                                                              |   |  |

| Exception Vector                                              |                                                                     |                                                                                                 |                                                                                                                                                              |   |  |

| Exception vector memory:                                      | onchip_memory2_0.s1<br>0x00000020                                   | •                                                                                               |                                                                                                                                                              |   |  |

| Exception vector offset:<br>Exception vector:                 | 0×01002020                                                          |                                                                                                 |                                                                                                                                                              |   |  |

IN QUARTUX2 compiled successfully , when I creating BSP in eclipse nios2 than following error coming.

Error coming while I am creating bsp for project.

Entry section mapping not created because reset memory location not located at base address 0x1011040.

Error :altera hal linker generator :the section mapping entry is missing.

Error :altera hal linker generator :Required linker section mapping do not exist:[entry].

| Nios II - TEST1/hello_world_s                       | 🐣 BSP Editor - D:\hsr_prp\uart_ALL_led_ELF_SOP\software\hal_bsp\settings.bsp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                      |  |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| File Edit Source Refactor                           | File Edit Tools Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                      |  |  |  |  |  |

| 1 <b>1 - 1</b> 6 6 6 6 6                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                      |  |  |  |  |  |

| Project Explorer X<br>S CEST1<br>C CEST1_BSP [uart] | SOPC Information file: \uart.sopcinfo         CPU name: nois2_gays_0         Operating system: Altera HAL         BSP target directory: .\         Settings         Common         hal         sys_ck_timer         - timestamp_timer         - stdut         - stdut         - stdut         - enable_gropfor         - enable_gropficate         - enable_gropficate         - enable_gropficate         - enable_gropficate         - enable_gropficate         - enable_gropficate         - enable_motive         - enable_motive      < | Image: Second state     Image: Second state       z     N       alt_stdio.h       em.h       o.h       TCHES_BASE_ADDRESS       BASE_ADDRESS       BASE_ADDRESS1       n(void) : int |  |  |  |  |  |

|                                                     | Octor in apping not created because reset memory region not located at base address: 0x1011040 [Error] altera_hal_lnkerx_generator: The section mapping ".entry" is missing. [Error] altera_hal_lnkerx_generator: Required linker section mappings do not exist: "[.entry]"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ₫ Q + C + = = = = = = = = = = = = = = = = =                                                                                                                                          |  |  |  |  |  |

| -                                                   | Generate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ,                                                                                                                                                                                    |  |  |  |  |  |

| 📀 ⋵ 📋                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6:23 PM<br>6:23 PM<br>12/26/2017                                                                                                                                                     |  |  |  |  |  |