# Intel® Desktop Boards D915GAV/D915GAG Technical Product Specification

December 2004

Order Number: C68600-002

The Intel<sup>®</sup> Desktop Board D915GAV/D915GAG may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in the Intel Desktop Board D915GAV/D915GAG Specification Update.

# **Revision History**

| Revision | Revision History                                                                                       | Date          |

|----------|--------------------------------------------------------------------------------------------------------|---------------|

| -001     | First release of the Intel <sup>®</sup> Desktop Board D915GAV/D915GAG Technical Product Specification. | June 2004     |

| -002     | Second release of the Intel Desktop Board D915GAV/D915GAG Technical Product Specification.             | December 2004 |

This product specification applies to only standard Intel Desktop Boards D915GAV and D915GAV with BIOS identifier EV91510A.86A.

Changes to this specification will be published in the Intel Desktop Board D915GAV/D915GAG Specification Update before being incorporated into a revision of this document.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel<sup>®</sup> desktop boards may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 5937 Denver, CO 80217-9808

or call in North America 1-800-548-4725, Europe 44-0-1793-431-155, France 44-0-1793-421-777, Germany 44-0-1793-421-333, other Countries 708-296-9333.

Intel, Pentium, and Celeron are registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\* Other names and brands may be claimed as the property of others.

This Technical Product Specification (TPS) specifies the board layout, components, connectors, power and environmental requirements, and the BIOS for these Intel® Desktop Boards: D915GAV and D915GAG. It describes the standard product and available manufacturing options.

# **Intended Audience**

The TPS is intended to provide detailed, technical information about the Desktop Boards D915GAV and D915GAG and their components to the vendors, system integrators, and other engineers and technicians who need this level of information. It is specifically not intended for general audiences.

# What This Document Contains

#### Chapter Description

- 1 A description of the hardware used on the Desktop Boards D915GAV and **D915GAG**

- 2 A map of the resources of the Desktop Boards

- 3 The features supported by the BIOS Setup program

- 4 A description of the BIOS error messages, beep codes, and POST codes

# **Typographical Conventions**

This section contains information about the conventions used in this specification. Not all of these symbols and abbreviations appear in all specifications of this type.

# Notes, Cautions, and Warnings

#### NOTE ~~

Notes call attention to important information.

# **\*** INTEGRATOR'S NOTES

Integrator's notes are used to call attention to information that may be useful to system integrators.

###

Cautions are included to help you avoid damaging hardware or losing data.

#

Warnings indicate conditions, which if not observed, can cause personal injury.

### **Other Common Notation**

| #         | Used after a signal name to identify an active-low signal (such as USBP0#)                                                                                                                                                                                                                                                            |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| (NxnX)    | When used in the description of a component, N indicates component type, xn are the relative coordinates of its location on the Desktop Boards D915GAV and D915GAG, and X is the instance of the particular part at that general location. For example, J5J1 is a connector, located at 5J. It is the first connector in the 5J area. |  |

| GB        | Gigabyte (1,073,741,824 bytes)                                                                                                                                                                                                                                                                                                        |  |

| GB/sec    | Gigabytes per second                                                                                                                                                                                                                                                                                                                  |  |

| KB        | Kilobyte (1024 bytes)                                                                                                                                                                                                                                                                                                                 |  |

| Kbit      | Kilobit (1024 bits)                                                                                                                                                                                                                                                                                                                   |  |

| kbits/sec | c 1000 bits per second                                                                                                                                                                                                                                                                                                                |  |

| MB        | Megabyte (1,048,576 bytes)                                                                                                                                                                                                                                                                                                            |  |

| MB/sec    | /sec Megabytes per second                                                                                                                                                                                                                                                                                                             |  |

| Mbit      | Megabit (1,048,576 bits)                                                                                                                                                                                                                                                                                                              |  |

| Mbit/sec  | /sec Megabits per second                                                                                                                                                                                                                                                                                                              |  |

| xxh       | An address or data value ending with a lowercase h indicates a hexadecimal value.                                                                                                                                                                                                                                                     |  |

| x.x V     | Volts. Voltages are DC unless otherwise specified.                                                                                                                                                                                                                                                                                    |  |

| *         | This symbol is used to indicate third-party brands and names that are the property of their respective owners.                                                                                                                                                                                                                        |  |

# 1 Product Description

| 1.1  | PCI Bus               | Terminology Change                                 | . 11 |

|------|-----------------------|----------------------------------------------------|------|

| 1.2  | Board D               | ifferences                                         | . 11 |

| 1.3  | Overview              | Ν                                                  | . 12 |

|      | 1.3.1                 | Feature Summary                                    | . 12 |

|      | 1.3.2                 | Manufacturing Options                              | . 13 |

|      | 1.3.3                 | Board Layouts                                      | . 14 |

|      | 1.3.4                 | Block Diagram                                      | . 18 |

| 1.4  | Online S              | Support                                            | . 19 |

| 1.5  | Process               | or                                                 | . 19 |

| 1.6  | System                | Memory                                             | . 20 |

|      | 1.6.1                 | Memory Configurations                              | . 22 |

| 1.7  | Intel <sup>®</sup> 91 | 5G Chipset                                         | .26  |

|      | 1.7.1                 | Intel 915G Graphics Subsystem                      | .26  |

|      | 1.7.2                 | USB                                                | . 28 |

|      | 1.7.3                 | IDE Support                                        | . 28 |

|      | 1.7.4                 | Real-Time Clock, CMOS SRAM, and Battery            | . 30 |

| 1.8  | PCI Exp               | ress Connectors                                    | . 30 |

| 1.9  | I/O Cont              | troller                                            | . 31 |

|      | 1.9.1                 | Serial Ports                                       | . 31 |

|      | 1.9.2                 | Parallel Port                                      |      |

|      | 1.9.3                 | Diskette Drive Controller                          |      |

|      | 1.9.4                 | Keyboard and Mouse Interface                       | . 32 |

| 1.10 |                       | ubsystem                                           |      |

|      | 1.10.1                | Audio Subsystem Software                           |      |

|      | 1.10.2                | Audio Connectors                                   |      |

|      | 1.10.3                | Intel <sup>®</sup> High Definition Audio Subsystem |      |

| 1.11 |                       | bsystem                                            |      |

|      | 1.11.1                | 10/100 Mbits/sec LAN Subsystem                     |      |

|      | 1.11.2                | Gigabit LAN Subsystem                              |      |

|      | 1.11.3                | Alert Standard Format (ASF) Support                |      |

|      | 1.11.4                | LAN Subsystem Software                             |      |

| 1.12 |                       | re Management Subsystem                            |      |

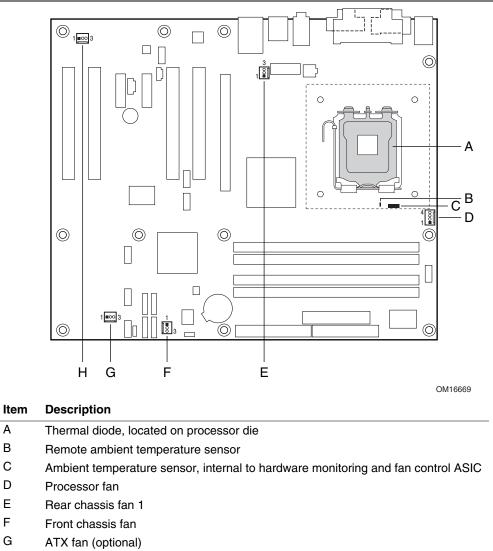

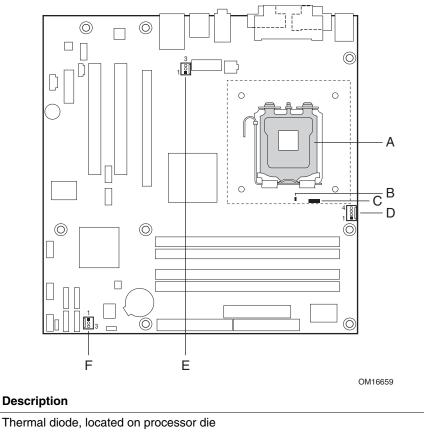

|      | 1.12.1                | Hardware Monitoring and Fan Control ASIC           |      |

|      | 1.12.2                | Thermal Monitoring                                 |      |

|      | 1.12.3                | Fan Monitoring                                     |      |

|      | 1.12.4                | Chassis Intrusion and Detection                    |      |

| 1.13 |                       | Nanagement                                         |      |

|      | 1.13.1                | ACPI                                               |      |

|      | 1.13.2                | Hardware Support                                   |      |

| 1.14 |                       | Platform Module (Optional)                         |      |

|      | 1.14.1                | System Requirements                                |      |

|      | 1.14.2                | Warning of Potential Data Loss                     |      |

|      | 1.14.3                | Security Precautions                               | . 49 |

|   |            | 1.14.4<br>1.14.5<br>1.14.6<br>1.14.7<br>1.14.8 | Trusted Platform Module Ownership<br>Enabling the Trusted Platform Module<br>Assuming Trusted Platform Module Ownership<br>Recovery Procedures<br>Clearing Trusted Platform Module Ownership | 51<br>51<br>52 |

|---|------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|   |            | 1.14.9                                         | Software Support                                                                                                                                                                             | 54             |

| 2 | Тес        | hnical F                                       | Reference                                                                                                                                                                                    |                |

|   | 2.1        |                                                | tion                                                                                                                                                                                         |                |

|   | 2.2        |                                                | Resources                                                                                                                                                                                    |                |

|   |            | 2.2.1                                          | Addressable Memory                                                                                                                                                                           |                |

|   | 0.0        | 2.2.2                                          | Memory Map                                                                                                                                                                                   |                |

|   | 2.3        |                                                | annels                                                                                                                                                                                       |                |

|   | 2.4<br>2.5 |                                                | D Map<br>Ifiguration Space Map                                                                                                                                                               |                |

|   | 2.5<br>2.6 |                                                |                                                                                                                                                                                              |                |

|   | 2.7        |                                                | ventional Interrupt Routing Map                                                                                                                                                              |                |

|   | 2.8        |                                                | ors                                                                                                                                                                                          |                |

|   |            | 2.8.1                                          | Back Panel Connectors                                                                                                                                                                        |                |

|   |            | 2.8.2                                          | Component-side Connectors                                                                                                                                                                    |                |

|   | 2.9        | Jumper                                         | Block                                                                                                                                                                                        | 77             |

|   | 2.10       | Mechani                                        | ical Considerations                                                                                                                                                                          |                |

|   |            | 2.10.1                                         | D915GAV Board Form Factor                                                                                                                                                                    |                |

|   |            | 2.10.2                                         | D915GAG Board Form Factor                                                                                                                                                                    |                |

|   |            | 2.10.3                                         | I/O Shield                                                                                                                                                                                   |                |

|   | 2.11       |                                                | al Considerations                                                                                                                                                                            |                |

|   |            | 2.11.1                                         | DC Loading                                                                                                                                                                                   |                |

|   |            | 2.11.2                                         | Add-in Board Considerations                                                                                                                                                                  |                |

|   |            | 2.11.3                                         | Fan Connector Current Capability                                                                                                                                                             |                |

|   | 0 10       | 2.11.4                                         | Power Supply Considerations                                                                                                                                                                  |                |

|   |            |                                                | Considerations                                                                                                                                                                               |                |

|   |            |                                                | nental                                                                                                                                                                                       |                |

|   |            |                                                | bry Compliance                                                                                                                                                                               |                |

|   | 2.10       |                                                | Safety Regulations                                                                                                                                                                           |                |

|   |            | 2.15.2                                         | EMC Regulations                                                                                                                                                                              |                |

|   |            | 2.15.3                                         | European Union Declaration of Conformity Statement                                                                                                                                           |                |

|   |            | 2.15.4                                         | Product Ecology Statements                                                                                                                                                                   | 89             |

|   |            | 2.15.5                                         | Product Certification Markings (Board Level)                                                                                                                                                 | 90             |

| 3 | Ove        | rview o                                        | of BIOS Features                                                                                                                                                                             |                |

| - | 3.1        |                                                | tion                                                                                                                                                                                         | 91             |

|   | 3.2        |                                                | ash Memory Organization                                                                                                                                                                      |                |

|   | 3.3        |                                                | e Configuration                                                                                                                                                                              |                |

|   |            | 3.3.1                                          | PCI Autoconfiguration                                                                                                                                                                        |                |

|   |            | 3.3.2                                          | PCI IDE Support                                                                                                                                                                              |                |

|   | 3.4        |                                                | Management BIOS (SMBIOS)                                                                                                                                                                     |                |

|   | 3.5        | •                                              | USB Support                                                                                                                                                                                  |                |

| 3.6 | BIOS U  | Ipdates                                                | 94 |

|-----|---------|--------------------------------------------------------|----|

|     | 3.6.1   | Language Support                                       | 94 |

|     | 3.6.2   | Custom Splash Screen                                   | 94 |

| 3.7 | Boot O  | ptions                                                 |    |

|     | 3.7.1   | CD-ROM Boot                                            |    |

|     | 3.7.2   | Network Boot                                           |    |

|     | 3.7.3   | Booting Without Attached Devices                       |    |

|     | 3.7.4   | Changing the Default Boot Device During POST           |    |

| 3.8 | Fast Bo | poting Systems with Intel <sup>®</sup> Rapid BIOS Boot |    |

|     | 3.8.1   | Peripheral Selection and Configuration                 |    |

|     | 3.8.2   | Intel Rapid BIOS Boot                                  |    |

| 3.9 | BIOS S  | Security Features                                      |    |

|     |         | 2                                                      |    |

# 4 Error Messages and Beep Codes

| 4.1 | BIOS Error Messages            |  |

|-----|--------------------------------|--|

|     | Port 80h POST Codes            |  |

| 4.3 | Bus Initialization Checkpoints |  |

| 4.4 | Speaker                        |  |

| 4.5 | BIOS Beep Codes                |  |

# Figures

| 1.  | D915GAV Board Components                                                     | 14 |

|-----|------------------------------------------------------------------------------|----|

| 2.  | D915GAG Board Components                                                     | 16 |

| 3.  | Block Diagram                                                                |    |

| 4.  | Memory Channel and DIMM Configuration                                        |    |

| 5.  | Dual Channel (Interleaved) Mode Configuration with Two DIMMs                 | 23 |

| 6.  | Dual Channel (Interleaved) Mode Configuration with Three DIMMs               | 23 |

| 7.  | Dual Channel (Interleaved) Mode Configuration with Four DIMMs                | 24 |

| 8.  | Single Channel (Asymmetric) Mode Configuration with One DIMM                 | 25 |

| 9.  | Single Channel (Asymmetric) Mode Configuration with Three DIMMs              |    |

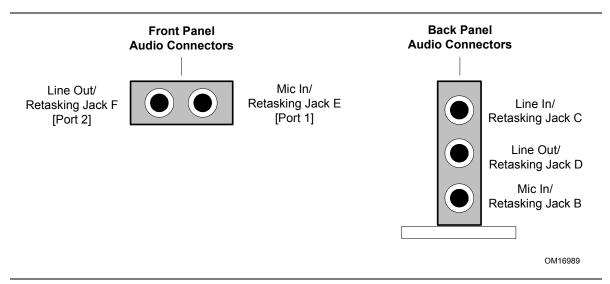

| 10. | Front/Back Panel Audio Connector Options for High Definition Audio Subsystem |    |

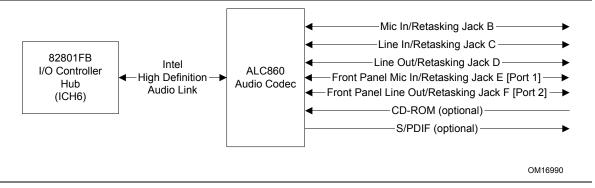

| 11. | High Definition Audio Subsystem Block Diagram                                |    |

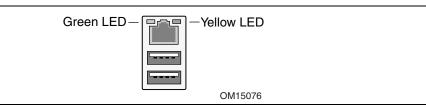

| 12. | LAN Connector LED Locations                                                  |    |

| 13. | LAN Connector LED Locations                                                  | 37 |

| 14. | Thermal Monitoring for D915GAV Board                                         | 39 |

| 15. | Thermal Monitoring for D915GAG Board                                         |    |

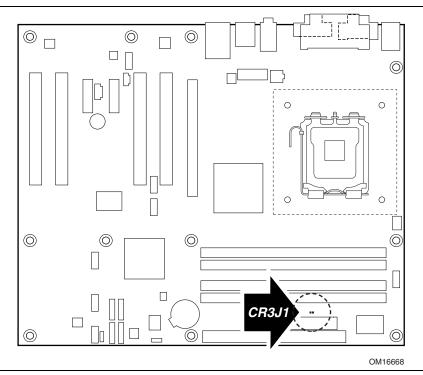

| 16. | Location of the Standby Power Indicator LED                                  | 47 |

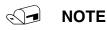

| 17. | Detailed System Memory Address Map                                           | 56 |

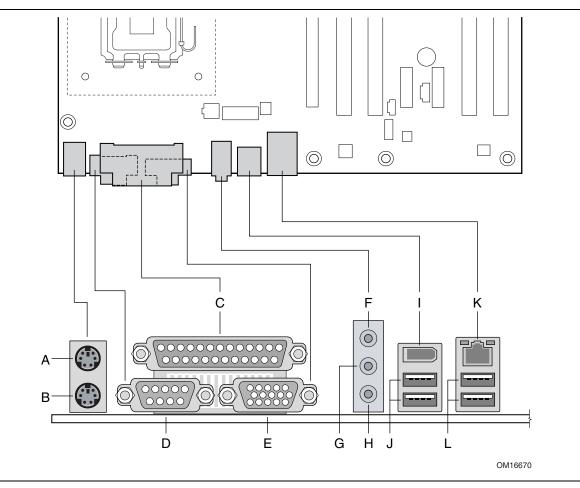

| 18. | Back Panel Connectors                                                        |    |

| 19. | D915GAV Board Component-side Connectors                                      |    |

| 20. | D915GAG Board Component-side Connectors                                      |    |

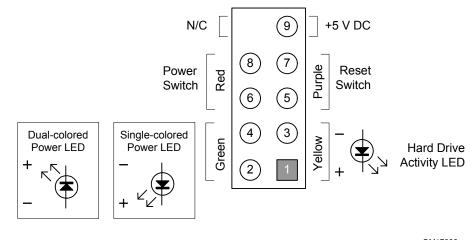

| 21. | Connection Diagram for Front Panel Connector                                 |    |

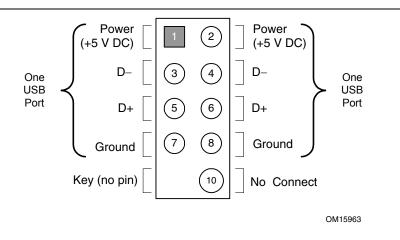

| 22. | Connection Diagram for Front Panel USB Connectors                            | 76 |

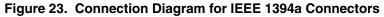

| 23. | Connection Diagram for IEEE 1394a Connectors                                 |    |

| 24. | Location of the Jumper Block                                                 | 77 |

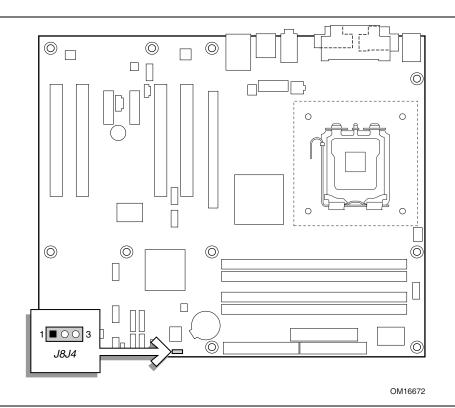

| 25. | D915GAV Board Dimensions                                                     | 78 |

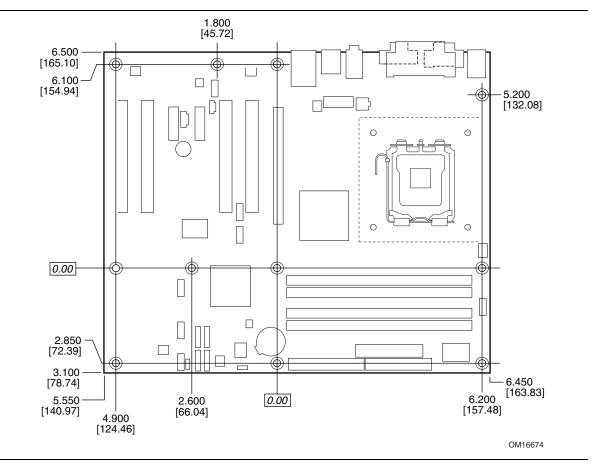

| 26. | D915GAG Board Dimensions                                                     | 79 |

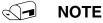

| 27. | I/O Shield Dimensions                           | .80 |

|-----|-------------------------------------------------|-----|

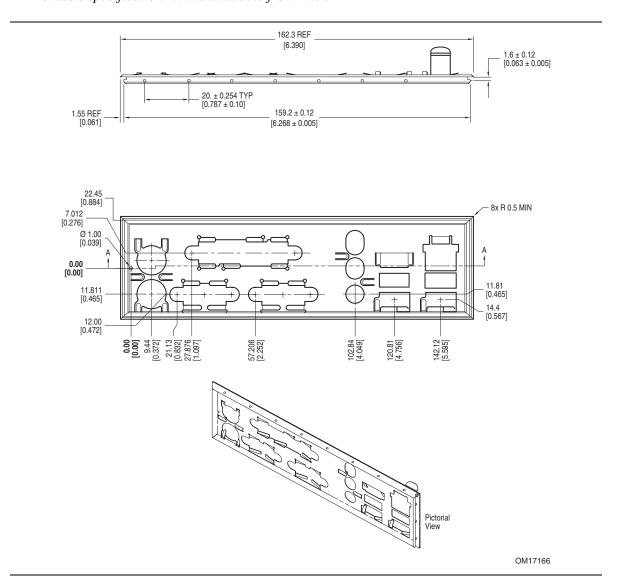

| 28. | Processor Heatsink for Omni-directional Airflow | .83 |

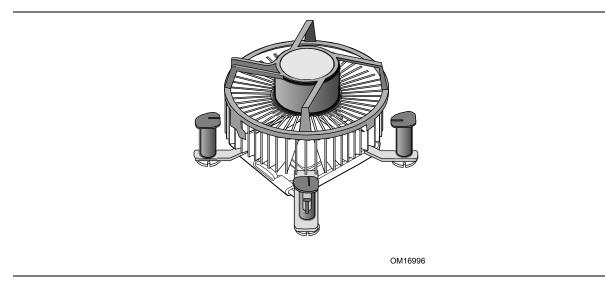

| 29. | Localized High Temperature Zones                | .84 |

### Tables

| 1.  | Summary of Board Differences                                 | .11  |

|-----|--------------------------------------------------------------|------|

| 2.  | Feature Summary                                              |      |

| 3.  | Manufacturing Options                                        |      |

| 4.  | D915GAV Board Components Shown in Figure 1                   |      |

| 5.  | D915GAG Board Components Shown in Figure 2                   |      |

| 6.  | Supported System Bus Frequency and Memory Speed Combinations |      |

| 7.  | Supported Memory Configurations                              |      |

| 8.  | LAN Connector LED States                                     |      |

| 9.  | LAN Connector LED States                                     |      |

| 10. | Effects of Pressing the Power Switch                         |      |

| 11. | Power States and Targeted System Power                       |      |

| 12. | Wake-up Devices and Events                                   |      |

| 13. | System Memory Map                                            |      |

| 14. | DMA Channels                                                 |      |

| 15. | I/O Map                                                      |      |

| 16. | PCI Configuration Space Map                                  |      |

| 17. | Interrupts                                                   |      |

| 18. | PCI Interrupt Routing Map                                    |      |

| 19. | Back Panel Connectors Shown in Figure 18                     |      |

| 20. | Component-side Connectors Shown in Figure 19                 |      |

| 21. | Component-side Connectors Shown in Figure 20                 |      |

| 22. | S/PDIF Connector (Optional)                                  | .70  |

| 23. | ATAPI CD-ROM Connector (Optional)                            |      |

| 24. | Front Panel Audio Connector                                  |      |

| 25. | Serial Port B Connector (optional)                           | .70  |

| 26. | Chassis Intrusion Connector                                  | .70  |

| 27. | SCSI Hard Drive Activity LED Connector (Optional)            | .71  |

| 28. | Serial ATA Connectors                                        | .71  |

| 29. | Processor Fan Connector                                      | .71  |

| 30. | Chassis Fan Connectors                                       | .71  |

| 31. | Main Power Connector                                         | .72  |

| 32. | ATX12V Power Connector                                       | .73  |

| 33. | Alternate Power Connector                                    | .73  |

| 34. | Auxiliary Front Panel Power/Sleep LED Connector              | .74  |

| 35. | Front Panel Connector                                        |      |

| 36. | States for a One-Color Power LED                             | .75  |

| 37. | States for a Two-Color Power LED                             | .75  |

| 38. | BIOS Setup Configuration Jumper Settings                     | .77  |

| 39. | DC Loading Characteristics                                   |      |

| 40. | Fan Connector Current Capability                             | . 82 |

| 41. | Thermal Considerations for Components                        | . 85 |

| 42. | Environmental Specifications                                 | . 86 |

| Safety Regulations                           | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EMC Regulations                              | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Product Certification Markings               | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BIOS Setup Program Menu Bar                  | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BIOS Setup Program Function Keys             | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Boot Device Menu Options                     | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Supervisor and User Password Functions       | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BIOS Error Messages                          | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Uncompressed INIT Code Checkpoints           | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Boot Block Recovery Code Checkpoints         | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Runtime Code Uncompressed in F000 Shadow RAM |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Bus Initialization Checkpoints               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                              | Safety Regulations<br>EMC Regulations<br>Product Certification Markings<br>BIOS Setup Program Menu Bar<br>BIOS Setup Program Function Keys<br>Boot Device Menu Options<br>Supervisor and User Password Functions<br>BIOS Error Messages<br>Uncompressed INIT Code Checkpoints<br>Boot Block Recovery Code Checkpoints<br>Runtime Code Uncompressed in F000 Shadow RAM<br>Bus Initialization Checkpoints<br>Upper Nibble High Byte Functions<br>Lower Nibble High Byte Functions<br>Beep Codes |

Intel Desktop Board D915GAV/D915GAG Technical Product Specification

# What This Chapter Contains

| 1.1  | PCI Bus Terminology Change         | 11 |

|------|------------------------------------|----|

| 1.2  | Board Differences                  |    |

| 1.3  | Overview                           |    |

| 1.4  | Online Support                     | 19 |

| 1.5  | Processor                          |    |

| 1.6  | System Memory                      | 20 |

| 1.7  | Intel® 915G Chipset                | 26 |

| 1.8  | PCI Express Connectors             | 30 |

| 1.9  | I/O Controller                     | 31 |

| 1.10 | Audio Subsystem                    | 32 |

| 1.11 | LAN Subsystem                      | 35 |

|      | Hardware Management Subsystem      |    |

| 1.13 | Power Management                   | 41 |

| 1.14 | Trusted Platform Module (Optional) | 48 |

|      |                                    |    |

# 1.1 PCI Bus Terminology Change

Previous generations of Intel<sup>®</sup> Desktop Boards used an add-in card connector referred to as PCI. This generation of Intel Desktop Boards adds a new technology for add-in cards: PCI Express. The 32-bit parallel bus previously referred to as PCI is now called PCI Conventional.

# **1.2 Board Differences**

This TPS describes these Intel Desktop Boards: D915GAV and D915GAG. The Desktop Boards are identical with the exception of the items listed in Table 1.

|                                                | D915GAV                                                  | D915GAG                                                                                                                                                                |

|------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Form factor                                    | ATX                                                      | microATX                                                                                                                                                               |

| PCI Conventional Bus<br>add-in card connectors | Four                                                     | Two                                                                                                                                                                    |

| PCI Express x1 bus add-<br>in card connectors  | Тwo                                                      | One                                                                                                                                                                    |

| Chassis fan connectors                         | Three: front chassis, rear chassis 1, and rear chassis 2 | Two: front chassis and rear chassis                                                                                                                                    |

| LAN configuration                              | 10/100 Mbits/sec LAN subsystem only                      | <ul> <li>One of the following:</li> <li>Gigabit (10/100/1000 Mbits/sec)<br/>LAN subsystem</li> <li>10/100 Mbits/sec LAN subsystem</li> <li>No LAN subsystem</li> </ul> |

Table 1. Summary of Board Differences

### NOTE

Most of the illustrations in this document show only the Desktop Board D915GAV. When there are significant differences between the two Desktop Boards, illustrations of both boards are provided.

# 1.3 Overview

### 1.3.1 Feature Summary

Table 2 summarizes the major features of the Desktop Boards D915GAV and D915GAG.

| Form Factor | <ul> <li>D915GAV: ATX (12.00 inches by 9.60 inches [304.80 millimeters by<br/>243.84 millimeters])</li> </ul>            |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

|             | D915GAG: microATX Form Factor (9.60 inches by 9.60 inches [243.84 millimeters by 243.84 millimeters])                    |  |  |  |

| Processor   | Support for an Intel <sup>®</sup> Pentium <sup>®</sup> 4 processor in an LGA775 socket with an 800 or 533 MHz system bus |  |  |  |

| Memory      | Four DDR SDRAM Dual Inline Memory Module (DIMM) sockets                                                                  |  |  |  |

|             | Support for DDR 400 MHz and DDR 333 MHz DIMMs                                                                            |  |  |  |

|             | Support for up to 4 GB of system memory                                                                                  |  |  |  |

| Chipset     | Intel <sup>®</sup> 915G Chipset, consisting of:                                                                          |  |  |  |

|             | Intel <sup>®</sup> 82915G Graphics Memory Controller Hub (GMCH)                                                          |  |  |  |

|             | Intel <sup>®</sup> 82801FB I/O Controller Hub (ICH6)                                                                     |  |  |  |

|             | • 4 Mbit Firmware Hub (FWH)                                                                                              |  |  |  |

| Video       | Intel <sup>®</sup> GMA900 onboard graphics subsystem                                                                     |  |  |  |

| Audio       | Intel® High Definition Audio subsystem using the Realtek ALC860 audio codec                                              |  |  |  |

| I/O Control | LPC Bus I/O controller                                                                                                   |  |  |  |

| USB         | Support for USB 2.0 devices                                                                                              |  |  |  |

| Peripheral  | Eight USB ports                                                                                                          |  |  |  |

| Interfaces  | One serial port                                                                                                          |  |  |  |

|             | One parallel port                                                                                                        |  |  |  |

|             | Four Serial ATA interfaces                                                                                               |  |  |  |

|             | One Parallel ATA IDE interface with UDMA 33, ATA-66/100 support                                                          |  |  |  |

|             | One diskette drive interface                                                                                             |  |  |  |

|             | <ul> <li>PS/2* keyboard and mouse ports</li> </ul>                                                                       |  |  |  |

| LAN Support | D915GAV: 10/100 Mbits/sec LAN subsystem using the Intel® 82562EZ Platform LAN Connect (PLC) device                       |  |  |  |

|             | • D915GAG: Refer to Table 3 on page 13 for a description of LAN subsystem options.                                       |  |  |  |

| BIOS        | Intel/AMI BIOS (resident in the 4 Mbit FWH)                                                                              |  |  |  |

|             | Support for Advanced Configuration and Power Interface (ACPI), Plug and Play, and SMBIOS                                 |  |  |  |

Table 2.

Feature Summary

continued

| Expansion           | • PCI Conventional bus connectors (four on the D915GAV; two on the D915GAG)        |  |  |  |

|---------------------|------------------------------------------------------------------------------------|--|--|--|

| Capabilities        | PCI Express x1 bus add-in card connectors (two on the D915GAV; one on the D915GAG) |  |  |  |

|                     | One PCI Express x16 bus add-in card connector (both boards)                        |  |  |  |

| Instantly Available | Support for PCI Local Bus Specification Revision 2.2                               |  |  |  |

| PC Technology       | <ul> <li>Support for PCI Express Revision 1.0a</li> </ul>                          |  |  |  |

|                     | Suspend to RAM support                                                             |  |  |  |

|                     | Wake on PCI, RS-232, front panel, PS/2 devices, and USB ports                      |  |  |  |

| Hardware Monitor    | Hardware monitoring and fan control ASIC                                           |  |  |  |

| Subsystem           | Voltage sense to detect out of range power supply voltages                         |  |  |  |

|                     | Thermal sense to detect out of range thermal values                                |  |  |  |

|                     | Three fan connectors                                                               |  |  |  |

|                     | Three fan sense inputs used to monitor fan activity                                |  |  |  |

|                     | Fan speed control                                                                  |  |  |  |

Table 2.

Feature Summary (continued)

### 1.3.2 Manufacturing Options

Table 3 describes the manufacturing options on the Desktop Boards D915GAV and D915GAG. Not every manufacturing option is available in all marketing channels. Please contact your Intel representative to determine which manufacturing options are available to you.

| Module (TPM)<br>For information abo          | put Refer to                                                                                                                                   |  |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Trusted Platform                             | A component that enhances platform security                                                                                                    |  |  |  |

| S/PDIF Connector                             | A 1 x 3 connector (mounted on the component side of the board) that provides digita audio signals in S/PDIF format                             |  |  |  |

| Serial Port B                                | Second serial port accessible via a connector on the component side of the board                                                               |  |  |  |

| SCSI Hard Drive<br>Activity LED<br>Connector | Allows add-in hard drive controllers (SCSI or other) to use the same LED as the onboard IDE controller.                                        |  |  |  |

|                                              | No LAN subsystem                                                                                                                               |  |  |  |

|                                              | 10/100 Mbits/sec LAN subsystem using the Intel <sup>®</sup> 82562EZ Platform LAN Connect (PLC) device                                          |  |  |  |

|                                              | <ul> <li>Gigabit (10/100/1000 Mbits/sec) LAN subsystem using the Marvel* Yukon*<br/>88E8050 PCI Express Gigabit Ethernet Controller</li> </ul> |  |  |  |

| LAN subsystem                                | The D915GAG board provides one of the following:                                                                                               |  |  |  |

| IEEE-1394a<br>Interface                      | IEEE-1394a controller and three IEEE-1394a connectors (one back panel connecto two front-panel connectors)                                     |  |  |  |

| ATX fan<br>connector                         | Additional fan connector for use in larger chassis (D915GAV board only)                                                                        |  |  |  |

| ATAPI CD-ROM<br>Connector                    | A connector for attaching an internal CD-ROM drive to the onboard audio subsystem                                                              |  |  |  |

Table 3. Manufacturing Options

Available configurations for the Desktop Boards D915GAV and D915GAG

Section 1.4, page 19

# 1.3.3 Board Layouts

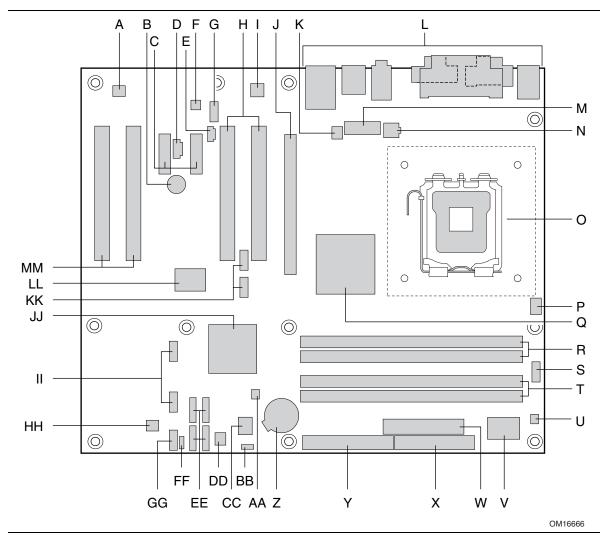

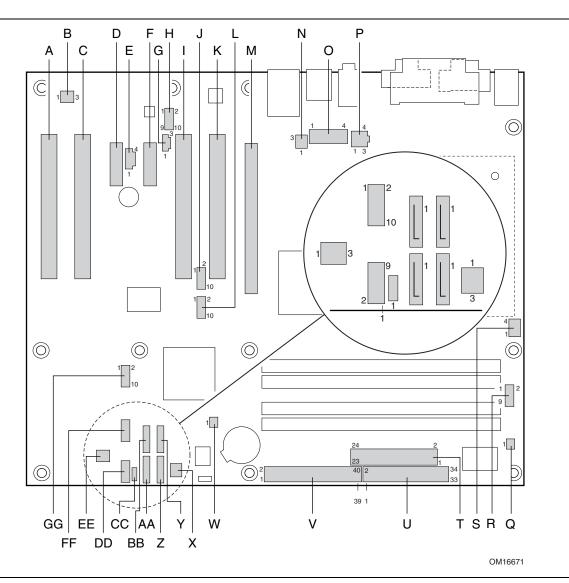

Figure 1 shows the location of the major components on the Desktop Board D915GAV.

Figure 1. D915GAV Board Components

Table 4 lists the components identified in Figure 1.

| Item/callout<br>from Figure 1 | Description                                  |  |  |  |

|-------------------------------|----------------------------------------------|--|--|--|

| A                             | Rear fan connector 2                         |  |  |  |

| В                             | Speaker                                      |  |  |  |

| С                             | PCI Express x1 bus add-in card connectors    |  |  |  |

| D                             | ATAPI CD-ROM connector (optional)            |  |  |  |

| E                             | S/PDIF connector (optional)                  |  |  |  |

| F                             | Realtek ALC860 audio codec                   |  |  |  |

| G                             | Front panel audio connector                  |  |  |  |

| Н                             | PCI Conventional bus add-in card connectors  |  |  |  |

| I                             | Ethernet PLC device (optional)               |  |  |  |

| J                             | PCI Express x16 bus add-in card connector    |  |  |  |

| К                             | Rear chassis fan connector 1                 |  |  |  |

| L                             | Back panel connectors                        |  |  |  |

| М                             | Alternate power connector                    |  |  |  |

| Ν                             | +12V power connector (ATX12V)                |  |  |  |

| 0                             | LGA775 processor socket                      |  |  |  |

| Р                             | Processor fan connector                      |  |  |  |

| Q                             | Intel 82915G GMCH                            |  |  |  |

| R                             | DIMM Channel A sockets                       |  |  |  |

| S                             | Serial port B connector (optional)           |  |  |  |

| Т                             | DIMM Channel B sockets                       |  |  |  |

| U                             | SCSI LED (optional)                          |  |  |  |

| V                             | I/O controller                               |  |  |  |

| W                             | Power connector                              |  |  |  |

| Х                             | Diskette drive connector                     |  |  |  |

| Y                             | Parallel ATE IDE connector                   |  |  |  |

| Z                             | Battery                                      |  |  |  |

| AA                            | Chassis intrusion connector                  |  |  |  |

| BB                            | BIOS Setup configuration jumper block        |  |  |  |

| CC                            | 4 Mbit Firmware Hub (FWH)                    |  |  |  |

| DD                            | Front chassis fan connector                  |  |  |  |

| EE                            | Serial ATA connectors                        |  |  |  |

| FF                            | Auxiliary front panel power LED connector    |  |  |  |

| GG                            | Front panel connector                        |  |  |  |

| HH                            | ATX fan connector (optional)                 |  |  |  |

| II                            | Front panel USB connector                    |  |  |  |

| JJ                            | Intel 82801FB I/O Controller Hub (ICH6)      |  |  |  |

| KK                            | Front panel IEEE-1394a connectors (optional) |  |  |  |

| LL                            | IEEE-1394a controller (optional)             |  |  |  |

| MM                            | PCI Conventional bus add-in card connectors  |  |  |  |

Table 4.

D915GAV Board Components Shown in Figure 1

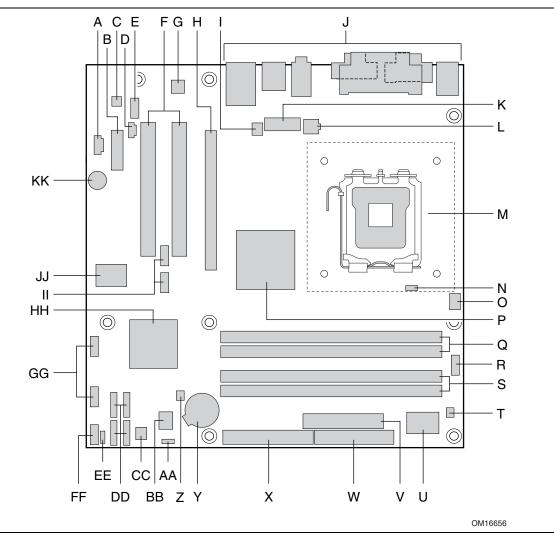

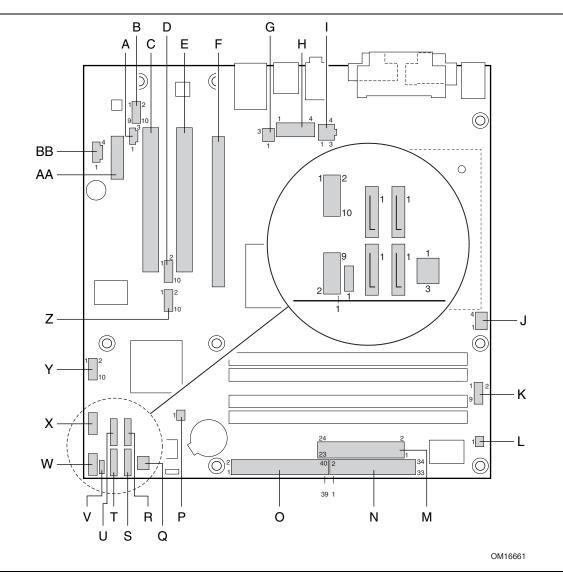

Figure 2 shows the location of the major components on the Desktop Board D915GAG.

Figure 2. D915GAG Board Components

Table 5 lists the components identified in Figure 2.

| Item/callout<br>from Figure 2 | Description                                  |  |  |

|-------------------------------|----------------------------------------------|--|--|

| A                             | ATAPI CD-ROM connector (optional)            |  |  |

| В                             | PCI Express x1 bus add-in card connectors    |  |  |

| С                             | Realtek ALC860 audio codec                   |  |  |

| D                             | S/PDIF connector (optional)                  |  |  |

| E                             | Front panel audio connector                  |  |  |

| F                             | PCI Conventional bus add-in card connectors  |  |  |

| G                             | Ethernet PLC device (optional)               |  |  |

| Н                             | PCI Express x16 bus add-in card connector    |  |  |

| I                             | Rear chassis fan connector                   |  |  |

| J                             | Back panel connectors                        |  |  |

| К                             | Alternate power connector                    |  |  |

| L                             | +12V power connector (ATX12V)                |  |  |

| М                             | LGA775 processor socket                      |  |  |

| N                             | Hardware monitoring and fan control ASIC     |  |  |

| 0                             | Processor fan connector                      |  |  |

| Р                             | Intel 82915G GMCH                            |  |  |

| Q                             | DIMM Channel A sockets                       |  |  |

| R                             | Serial port B connector (optional)           |  |  |

| S                             | DIMM Channel B sockets                       |  |  |

| Т                             | SCSI LED connector (optional)                |  |  |

| U                             | I/O controller                               |  |  |

| V                             | Power connector                              |  |  |

| W                             | Diskette drive connector                     |  |  |

| Х                             | Parallel ATE IDE connector                   |  |  |

| Y                             | Battery                                      |  |  |

| Z                             | Chassis intrusion connector                  |  |  |

| AA                            | BIOS Setup configuration jumper block        |  |  |

| BB                            | 4 Mbit Firmware Hub (FWH)                    |  |  |

| CC                            | Front chassis fan connector                  |  |  |

| DD                            | Serial ATA connectors                        |  |  |

| EE                            | Auxiliary front panel power LED connector    |  |  |

| FF                            | Front panel connector                        |  |  |

| GG                            | Front panel USB connector                    |  |  |

| НН                            | Intel 82801FB I/O Controller Hub (ICH6)      |  |  |

| II                            | Front panel IEEE-1394a connectors (optional) |  |  |

| JJ                            | IEEE-1394a controller (optional)             |  |  |

| KK                            | Speaker                                      |  |  |

Table 5.

D915GAG Board Components Shown in Figure 2

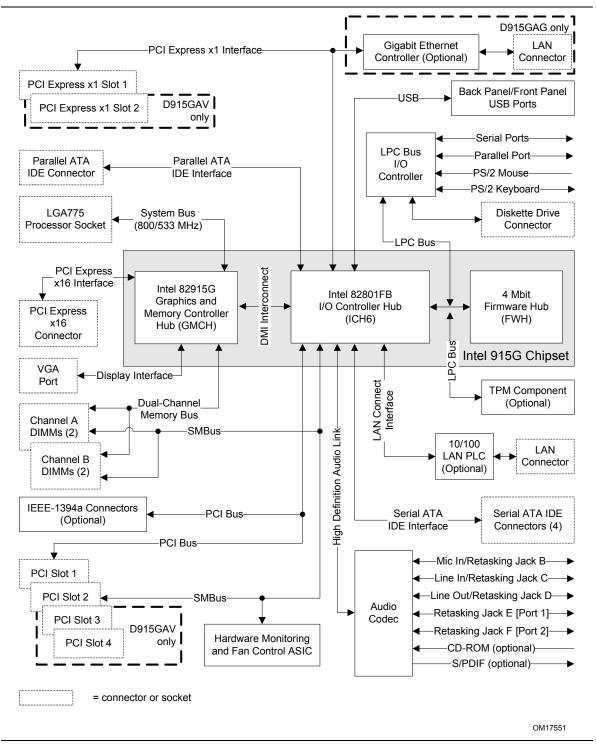

### 1.3.4 Block Diagram

Figure 3 is a block diagram of the major functional areas of the boards.

Figure 3. Block Diagram

# 1.4 Online Support

| To find information about                                     | Visit this World Wide Web site:                                |

|---------------------------------------------------------------|----------------------------------------------------------------|

| Intel Desktop Boards D915GAV and D915GAG under "Desktop Board | http://www.intel.com/design/motherbd                           |

| Products" or "Desktop Board Support"                          | http://support.intel.com/support/motherboards/desktop          |

| Available configurations for the Desktop<br>Board D915GAV     | http://developer.intel.com/design/motherbd/av/av_available.htm |

| Available configurations for the Desktop<br>Board D915GAG     | http://developer.intel.com/design/motherbd/ag/ag_available.htm |

| Processor data sheets                                         | http://www.intel.com/design/litcentr                           |

| ICH6 addressing                                               | http://developer.intel.com/design/chipsets/datashts            |

| Custom splash screens                                         | http://intel.com/design/motherbd/gen_indx.htm                  |

| Audio software and utilities                                  | http://www.intel.com/design/motherbd                           |

| LAN software and drivers                                      | http://www.intel.com/design/motherbd                           |

# 1.5 Processor

The boards are designed to support Intel Pentium 4 processors in an LGA775 processor socket with an 800 or 533 MHz system bus. See the Intel web site listed below for the most up-to-date list of supported processors.

| For information about                      | Refer to:                                           |

|--------------------------------------------|-----------------------------------------------------|

| Supported processors for the D915GAV board | http://www.intel.com/design/motherbd/av/av_proc.htm |

| Supported processors for the D915GAG board | http://www.intel.com/design/motherbd/ag/ag_proc.htm |

#

Use only the processors listed on web site above. Use of unsupported processors can damage the board, the processor, and the power supply.

# **\*** INTEGRATOR'S NOTE

- Use only ATX12V-compliant power supplies.

- *Refer to Table 6 on page 20 for a list of supported system bus frequency and memory speed combinations.*

| For information about   | Refer to                 |

|-------------------------|--------------------------|

| Power supply connectors | Section 2.8.2.2, page 72 |

# 1.6 System Memory

The boards have four DIMM sockets and support the following memory features:

- 2.5 V (only) DDR SDRAM DIMMs with gold-plated contacts

- Unbuffered, single-sided or double-sided DIMMs with the following restriction:

Double-sided DIMMS with x16 organization are not supported.

- 4 GB maximum total system memory. Refer to Section 2.2.1 on page 55 for information on the total amount of addressable memory.

- Minimum total system memory: 128 MB

- Non-ECC DIMMs

- Serial Presence Detect

- DDR 400 MHz and DDR 333 MHz SDRAM DIMMs

Table 6 lists the supported system bus frequency and memory speed combinations.

| Table 6. | Supported System Bus Frequency and Memory Speed Combinations |

|----------|--------------------------------------------------------------|

|----------|--------------------------------------------------------------|

| To use this type of DIMM | The processor's system bus frequency must be |  |

|--------------------------|----------------------------------------------|--|

| DDR 400                  | 800 MHz                                      |  |

| DDR 333 (Note)           | 800 or 533 MHz                               |  |

Note: When using an 800 MHz system bus frequency processor, DDR 333 memory is clocked at 320 MHz. This minimizes system latencies to optimize system throughput.

# NOTES

- *Remove the PCI Express x16 video card before installing or upgrading memory to avoid interference with the memory retention mechanism.*

- To be fully compliant with all applicable DDR SDRAM memory specifications, the board should be populated with DIMMs that support the Serial Presence Detect (SPD) data structure. This allows the BIOS to read the SPD data and program the chipset to accurately configure memory settings for optimum performance. If non-SPD memory is installed, the BIOS will attempt to correctly configure the memory settings, but performance and reliability may be impacted or the DIMMs may not function under the determined frequency.

| DIMM<br>Capacity | Configuration | SDRAM<br>Density | SDRAM Organization<br>Front-side/Back-side | Number of SDRAM<br>Devices |

|------------------|---------------|------------------|--------------------------------------------|----------------------------|

| 128 MB           | SS            | 256 Mbit         | 16 M x 16/empty                            | 4                          |

| 256 MB           | SS            | 256 Mbit         | 32 M x 8/empty                             | 8                          |

| 256 MB           | SS            | 512 Mbit         | 32 M x 16/empty                            | 4                          |

| 512 MB           | DS            | 256 Mbit         | 32 M x 8/32 M x 8                          | 16                         |

| 512 MB           | SS            | 512 Mbit         | 64 M x 8/empty                             | 8                          |

| 512 MB           | SS            | 1 Gbit           | 64 M x 16/empty                            | 4                          |

| 1024 MB          | DS            | 512 Mbit         | 64 M x 8/64 M x 8                          | 16                         |

| 1024 MB          | SS            | 1 Gbit           | 128 M x 8/empty                            | 8                          |

| 2048 MB          | DS            | 1 Gbit           | 128 M x 8/128 M x 8                        | 16                         |

Table 7 lists the supported DIMM configurations.

| Table 7. | Supported | Memory | Configurations |

|----------|-----------|--------|----------------|

|----------|-----------|--------|----------------|

Note: In the second column, "DS" refers to double-sided memory modules (containing two rows of SDRAM) and "SS" refers to single-sided memory modules (containing one row of SDRAM).

# **\*** INTEGRATOR'S NOTE

It is possible to install four 2048 MB (2 GB) modules for a total of 8 GB of system memory, however, only 4 GB of address space is available. Refer to Section 2.2.1, on page 55 for additional information on available memory.

# 1.6.1 Memory Configurations

The Intel 82915G GMCH supports two types of memory organization:

- **Dual channel (Interleaved) mode**. This mode offers the highest throughput for real world applications. Dual channel mode is enabled when the installed memory capacities of both DIMM channels are equal. Technology and device width can vary from one channel to the other but the installed memory capacity for each channel must be equal. If different speed DIMMs are used between channels, the slowest memory timing will be used.

- **Single channel (Asymmetric) mode**. This mode is equivalent to single channel bandwidth operation for real world applications. This mode is used when only a single DIMM is installed or the memory capacities are unequal. Technology and device width can vary from one channel to the other. If different speed DIMMs are used between channels, the slowest memory timing will be used.

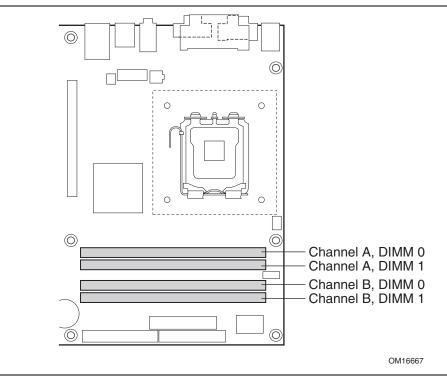

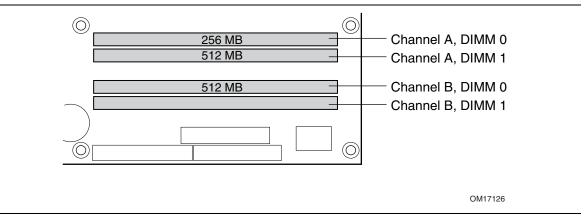

Figure 4 illustrates the memory channel and DIMM configuration.

# NOTE

The DIMMO sockets of both channels are blue. The DIMM1 sockets of both channels are black.

Figure 4. Memory Channel and DIMM Configuration

#### 1.6.1.1 Dual Channel (Interleaved) Mode Configurations

Figure 5 shows a dual channel configuration using two DIMMs. In this example, the DIMM0 (blue) sockets of both channels are populated with identical DIMMs.

Figure 5. Dual Channel (Interleaved) Mode Configuration with Two DIMMs

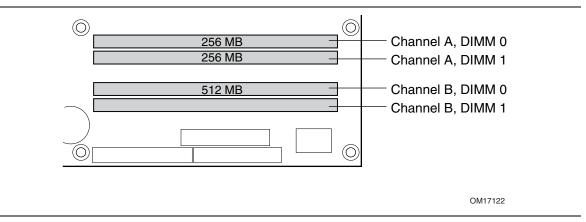

Figure 6 shows a dual channel configuration using three DIMMs. In this example, the combined capacity of the two DIMMs in Channel A equal the capacity of the single DIMM in the DIMM0 (blue) socket of Channel B.

Figure 6. Dual Channel (Interleaved) Mode Configuration with Three DIMMs

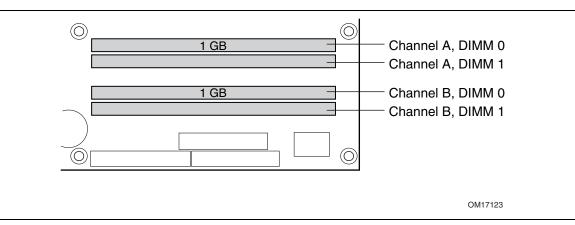

Figure 7 shows a dual channel configuration using four DIMMs. In this example, the combined capacity of the two DIMMs in Channel A equal the combined capacity of the two DIMMs in Channel B. Also, the DIMMs are matched between DIMM0 and DIMM1 of both channels.

Figure 7. Dual Channel (Interleaved) Mode Configuration with Four DIMMs

### 1.6.1.2 Single Channel (Asymmetric) Mode Configurations

### NOTE

Dual channel (Interleaved) mode configurations provide the highest memory throughput.

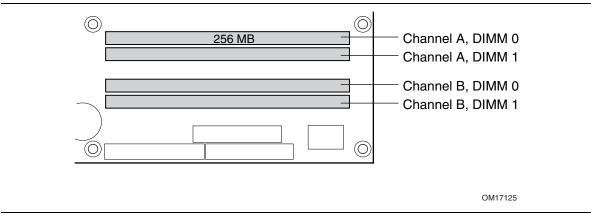

Figure 8 shows a single channel configuration using one DIMM. In this example, only the DIMM0 (blue) socket of Channel A is populated. Channel B is not populated.

Figure 8. Single Channel (Asymmetric) Mode Configuration with One DIMM

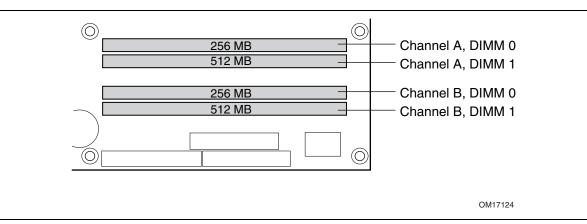

Figure 9 shows a single channel configuration using three DIMMs. In this example, the combined capacity of the two DIMMs in Channel A does not equal the capacity of the single DIMM in the DIMM0 (blue) socket of Channel B.

Figure 9. Single Channel (Asymmetric) Mode Configuration with Three DIMMs

# 1.7 Intel® 915G Chipset

The Intel 915G chipset consists of the following devices:

- Intel 82915G Graphics Memory Controller Hub (GMCH) with Direct Media Interface (DMI) interconnect

- Intel 82801FB I/O Controller Hub (ICH6) with DMI interconnect

- Firmware Hub (FWH)

The GMCH is a centralized controller for the system bus, the memory bus, the PCI Express bus, and the DMI interconnect. The ICH6 is a centralized controller for the board's I/O paths. The FWH provides the nonvolatile storage of the BIOS.

| For information about         | Refer to                    |

|-------------------------------|-----------------------------|

| The Intel 915G chipset        | http://developer.intel.com/ |

| Resources used by the chipset | Chapter 2                   |

### 1.7.1 Intel 915G Graphics Subsystem

The Intel 915G chipset contains two separate, mutually exclusive graphics options. Either the GMA900 graphics controller (contained within the 82915G GMCH) is used, or a PCI Express x16 add-in card can be used. When a PCI Express x16 add-in card is installed, the GMA900 graphics controller is disabled.

### 1.7.1.1 Intel<sup>®</sup> GMA900 Graphics Controller

The Intel GMA900 graphics controller features the following:

- Integrated graphics controller

- 32 bpp (Bits Per Pixel) graphics engine

- 333 MHz core frequency

- 256-bit 2-D engine

- 32-bit 3-D engine

- Motion video acceleration

- Pixel Shader 2.0

- 4-pixel pipes

- DirectX\* 9.0 Hardware Acceleration

- Software Vertex Shader

- Up to 2048 x 1536 at 75 Hz refresh

- With Advanced Digital Display 2 (ADD2) card support flat panel displays up to 2048 x 1536 at 75 Hz or digital CRTs/HDTV displays at 1920 x 1080 at 85 Hz

- High performance 3-D setup and render engine

- High quality/performance texture engine

- Display

- Integrated 24-bit 400 MHz RAMDAC

- DDC2B compliant interface

- Video

- Asynchronous dual monitor display with ADD2 card

- Hardware motion compensation for software MPEG2 decode

- Two multiplexed DVO port interfaces with 200 MHz pixel clocks using an ADD2 card

- Dynamic Video Memory Technology (DVMT) support up to 224 MB

- Intel<sup>®</sup> Zoom Utility

| For information about                     | Refer to                 |

|-------------------------------------------|--------------------------|

| DVMT                                      | Section 1.7.1.2, page 27 |

| Obtaining graphics software and utilities | Section 1.4, page 19     |

#### 1.7.1.2 Dynamic Video Memory Technology (DVMT)

DVMT enables enhanced graphics and memory performance through Direct AGP, and highly efficient memory utilization. DVMT ensures the most efficient use of available system memory for maximum 2-D/3-D graphics performance. Up to 224 MB of system memory can be allocated to DVMT on systems that have 512 MB or more of total system memory installed. Up to 128 MB can be allocated to DVMT on systems that have 256 MB but less than 512 MB of total installed system memory. Up to 64 MB can be allocated to DVMT when less than 256 MB of system memory is installed. DVMT returns system memory back to the operating system when the additional system memory is no longer required by the graphics subsystem.

DVMT will always use a minimal fixed portion of system physical memory (as set in the BIOS Setup program) for compatibility with legacy applications. An example of this would be when using VGA graphics under DOS. Once loaded, the operating system and graphics drivers allocate additional system memory to the graphics buffer as needed for performing graphics functions.

NOTE

The use of DVMT requires operating system driver support.

#### 1.7.1.3 Advanced Digital Display 2 (ADD2) Card Support

The GMCH routes two multiplexed DVO ports that are each capable of driving up to a 200 MHz pixel clock to the PCI Express x16 connector. The DVO ports can be paired for a dual channel configuration to support up to a 400 MHz pixel clock. When an ADD2 card is detected, the Intel GMA900 graphics controller is enabled and the PCI Express x16 connector is configured for DVO mode. DVO mode enables the DVO ports to be accessed by the ADD2 card. An ADD2 card can either be configured to support simultaneous display with the primary VGA display or can be configured to support dual independent display as an extended desktop configuration with different color depths and resolutions. ADD2 cards can be designed to support the following configurations:

- TV-Out (composite video)

- Transition Minimized Differential Signaling (TMDS) for DVI 1.0

- Low Voltage Differential Signaling (LVDS)

- Single device operating in dual channel mode

- VGA output

- HDTV output

### 1.7.1.4 Configuration Modes

A list of supported modes for the Intel GMA900 graphics controller is available as a downloadable document.

| For information about                 | Refer to                                             |