- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi at all! This is my first post.

I would like to have some advice to write the c code for my thesis. I have to use a NiosII_Stratix II_2s60. I have started from the example present in kits/nios2_51/examples/vhdl/niosII_StratixII_2s60. I've added in the project a 32bits counter (up counter) and a FIFO with this features: 32bits x 32768 words, almost full at 32000, almost empty < 1000). The counter is connected to FIFO and sends repeatedly bits to fill the FIFO that is connected to Nios. The FIFO is connected to NIOS through 3 ortogonal node that connect q[31..0] present in FIFO to in_pio3[7..0] present in Nios, the signal almost_full of FIFO is connected to in_pio1[7..0] present in Nios and the signal almost_empty of FIFO is connected to in_pio2[7..0] of Nios. The port q[31..0] of the counter is connected to data[31..0] of the FIFO. Starting from the simple socket server, using a lwip, i have to write a code for my project. The counter must sends bits continuously to FIFO but the counter must stops when the FIFO is almost full and when the FIFO is almost full the baud rate must be reduced. When the FIFO returns almost_empty the counter must restarts. How can i write this code? Could you give me some advice? Please help me to write this c code. Every advice is good for me. Thank you very much GreatingsLink Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The same task i am trying. Can you help in this project.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello SS5,

Welcome to the forum,

The board package contains demo code "OpenCore Plus evaluation of the Altera Triple-Speed Ethernet IP Core and supporting design example" This demo is a good place to start to get you up to speed with the TCP/IP stack.

Then, you can make several test projects for the various components of your project, test them with Modelsim and assemble your components to obtain your final project.

Please do understand that we can only try to help you with specific technical questions regarding problems where you are stuck.

Best Regards,

Johi.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

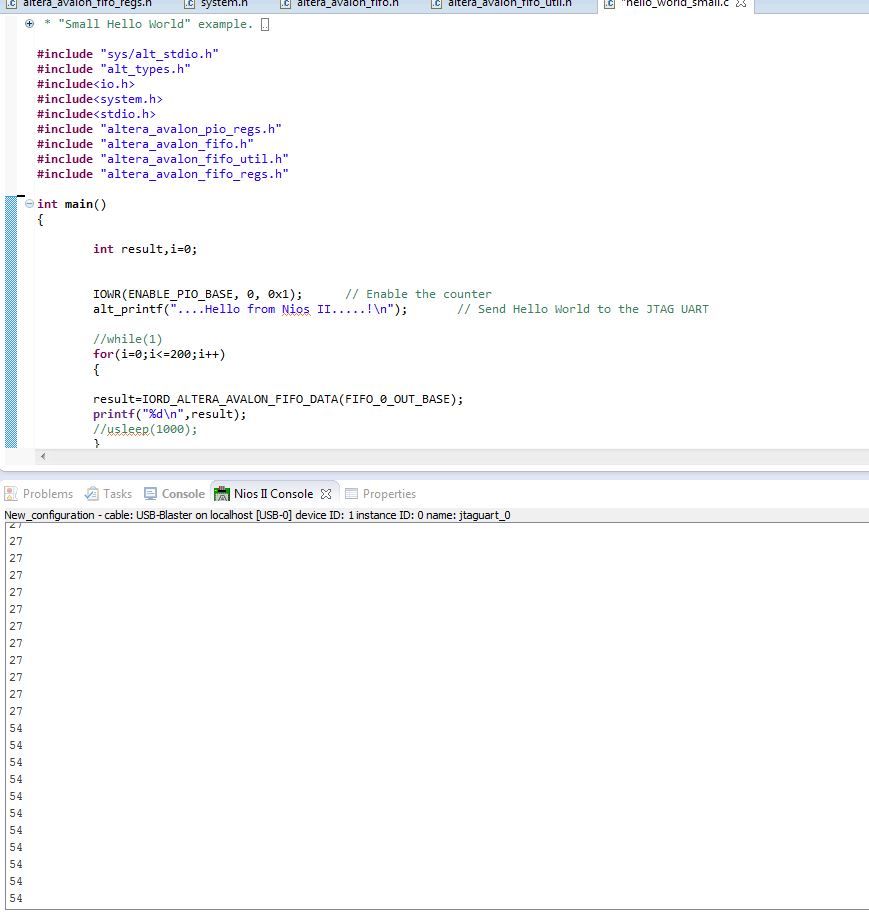

Hi,

I am stuck in one design for past 10 days. Working with Altera CYCLONE V FPGA board.

I am generating Trigger Signal for 500ns and 32-bit counter (Verilog), and at every (neck edge) positive edge of Trigger signal i need to collect and store that count data into reg (final_value).

Same thing, the counter is connected to FIFO and sends repeatedly bits to fill the FIFO that is connected to Nios.

Enable signal is given From PIO., and reading the counter data from NIOS

ISSUE: IN NIOS, same data printing continously for certain number of times.

Verilog Code

module Counter(

input clk, // 50Mhz

input enable,

input reset,

output reg[31:0] Final_value,

output reg trig

);

reg[31:0] counter_out;

reg [7:0] temp=0;

reg [31:0] counter_result;

wire temp1;

wire temp2;

always@(posedge clk)

begin

if(reset)

begin

trig<=0;

temp<=0;

counter_out<=0;

end

else if (enable==1'b1)

begin

counter_out<=counter_out+1;

temp<=temp+1;

if(temp==25)

begin

temp<=0;

trig<=~trig; /// Generating COunter

end

end

end

assign temp1=trig;

assign temp2=temp1&&clk;

always@(posedge temp2)

if(reset)

counter_result<=0;

else

begin

counter_result<=counter_result+1; // Increaming the Counter

end

always@(posedge trig) // Detecting Edge trig and storing into Final_value

if(reset)

Final_value<=0;

else

begin

Final_value<=counter_result;

end

endmoduleBlock Design

NIOS console

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page