- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

This post would seem to be near identical to:

But I have verified everything the replier suggested and the OP never confirmed that had worked.

I am using:

I had downloaded and installed and went through the various upgrades (both on installation of the PAR and in platform designer) to bring everything current. I have followed the application note exactly and programmed the FPGA. The blinking light is properly flashing away. During re-boot, the light blinks for a little bit and then somewhere along the way the motherboard hangs and the blinking light stops possibly indicating the motherboard is now holding everything in reset since it has failed enumeration.

I have done multiple attempts and tried to work through the problems myself, but am stuck and hope someone else has seen this and/or has a fix for it.

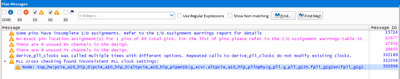

Here are the summary warnings during fitting.

I am attaching the project following the instructions as close to the letter as possible. I had to run clean project to get the files to fit. Any help would be appreciated.

Thanks,

Mil

- Tags:

- cyclone 10GX

- PCIe DMA

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for contacting Intel. I'm assigned to support request.

I'll investigate and get back to you soon. Thanks for your patience.

Best regards,

Hareesh B.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Hareesh,

As an update, I attempted to do Cyclone10GX_PCIeGen2x4_AVST_18_0.par today and it was successful in enumeration. I can't do much else since the DUT PC is a Linux box.

I have also successfully followed Intel® Cyclone® 10 GX CvP Initialization over PCI Express User Guide and was successful in programming the file and then compiling the Linux driver to install the rbf file.

I did do a factory reset when starting from Cyclone10GX_PCIeGen2x4_DMA_18_0 so I have confidence that the Evaluation board is working properly.

This reference design is where I want to start from and Linux is a requirement, so a lot of the other reference designs can only get me so far in proving the board works. They do not have the Linux driver nor application environment I would like to start evaluation from.

Please let me know if you need any more input from me. Hope to hear from you soon.

Thanks,

Mil

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am checking this issue. if you don't mind could you please check the pin assignment I am thinking problem with the pin assignment. please cross-check whether have you assigned it correctly or not.

Thank you,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Hareesh,

Thank you for looking into my problem. I am not sure what you mean by my assigning pins correctly. This is the reference design that has been downloaded directly from Intel from here:

https://www.intel.com/content/www/us/en/design-example/714945/cyclone-10-gx-pcie-gen2-x4-dma.html

The only changes I have made is that Quartus forces me to upgrade the IP. A quick view between the Avalon reference design and this one and I can agree that the assignments look different. But I don't know what is right as I am new to Altera/Intel. This was supposed to help me learn and in my humble opinion - this should have worked "as downloaded". It is listed as current on the Intel website. If the pin assignment is wrong, can you correct please and update the Intel content where this is downloaded from? Or at least correct and send me the right version.

Thanks in advance,

Mil

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

i will check and will update to you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You are using the new version of Quartus. the problem is that the example design can support the Quartus 18.0 version. In the newer version, you can see some more new features to that IP like new signals, data width, etc.. if you update the older designs ip's in a new version the signals of the new version ip's will be in an open state only. because of that, it shows errors. if you need to compile this please use Quarts 18.0 version only.

in the above image, you can see successfully compiled in Quartus 18.0.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As we do not receive any response from you on the previous question/reply/answer that we have provided. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I will most definitely not as accept this as a solution. How is this example project an example of anything else but obsolescence? Do I need to find 6 year old Linux, motherboards, etc as well? What would be the point of me exploring this obsolete project? What would it teach me (other than frustration and Intel's seemingly complete lack of support)?

Would it be possible to get a contact at Intel to return this development board for a full refund? There is no other PCIe DMA/Linux project. And since Intel's material is not maintained, I'm not sure how I can trust anything else? This link should have said with a big, bold red warning label - OBSOLETE - NOT RECOMMENDED FOR NEW DESIGNS.

https://www.intel.com/content/www/us/en/design-example/714945/cyclone-10-gx-pcie-gen2-x4-dma.html

If anyone else is reading this. Run!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page