- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

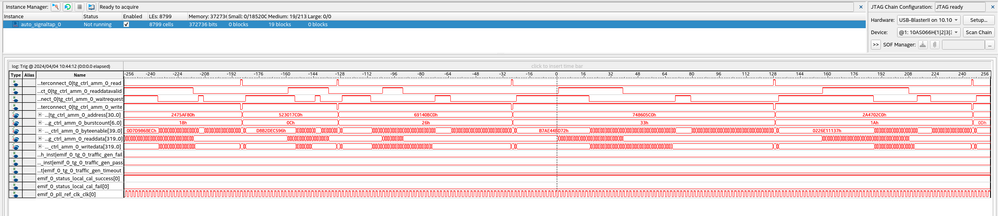

The development board I'm using is the Arria 10 SOC (10AS066N3F40E2SG). We attempted to use BTS for DDR4, but we were unable to carry out a flawless test. For further clarification, please refer to the attached image. There are a lot of read/write errors in the error control section.

Please look at, and if a fix is available, let us know.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I'm Adzim, application engineer will assist you in this thread.

I would need to verify some information to me get better understanding about this problem.

Please provide your respond to my questions below:

- What is the Quartus version that has been used/installed to test with BTS?

- How many board that are failing and passing the DDR4 test?

- Have you checked physically that the DDR4 HILO memory card is mounted perfectly?

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Adzim,

Thanks for the reply. Find inline response below-

Please provide your respond to my questions below:

- What is the Quartus version that has been used/installed to test with BTS?We are using Quartus pro 17.1 to test BTS as Quartus Version 15.1 is unavailable.

- How many board that are failing and passing the DDR4 test?We tested it with the single available board, and it failed.

- Have you checked physically that the DDR4 HILO memory card is mounted perfectly?This DDR4 daughter card was factory-installed when we bought the board. If you look at the previously attached screenshot, we can detect the RAM.

Note that the BTS is operating properly while the GPIO and LEDs are being tested.

Thanks,

Ganesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ganesh,

I can suggest to test the DDR4 interface with an EMIF example design.

You can refer to the Arria 10 EMIF User Guide for reference.

I have an EMIF example design that targeting Arria 10 SOC Development Board.

You test the design on the board and compare the result the you're acquired.

I will attach the design later.

Please be informed that I will be OOO starting tomorrow until 16/4/2024.

Expecting some delay to provide reply in this forum.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm attaching the design here.

This design was generated in Quartus Standard version 22.1.2.

You can follow the steps from the User Guide in section 1.8 and 1.9 to run the design.

There is a signal tap file that is ready to capture the signals of the DDR4 interface.

You can open Signal Tap Logic Analyzer from the Quartus's Tools tab and click on Run Analysis.

You should get similar result as picture below.

Please share your result of your test for observation.

Thanks,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks AdzimZM. We tested the provided DDR4 design. Traffic gen fail signal "1" was received. Please find attached the wave that was taken.

We upgraded the design and tested with Quartus Prime 22.4.

We also observe that the provided design not matches with FPGA-DDR4 configuration which is 2 GB DDR4 (256Mb x 72 x single rank) - ships with kit.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ganesh,

The example design that I have shared is targeting the HILO memory on HPS.

By default, the HILO memory on HPS is 1GB.

I will provide another example design that targeting HILO memory on FPGA (2GB).

Please verify that the development kit is set to default setting.

You may refer to Arria 10 SOC Development Kit User Guide in the link below.

3.2. Default Switch and Jumper Settings (intel.com)

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

FPGA HILO memory example design 2GB.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As we do not receive any response from you on the previous reply that we have provided, I now transition this thread to community support. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page