- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have recently acquired the Cyclone V GT Development Board (https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=167&No=843), my first Intel board moving over from Xilinx boards. I'm having trouble getting my clock signal to work. I'm trying to use a very simple design, toggling an LED based on a counter. I have also added a simple forwarding signal between buttons and LED's, to check that the upload is working correctly (it is).

However, my counter and LED simply do not seem to work. I've tried using multiple clock signals as identified on pages 2-20 and 2-21 in the reference manual (http://www.altera.com/literature/manual/rm_cvgt_fpga_dev_board.pdf), but no matter which one I choose, the output is the same (the led regOut is constantly lit, meaning a logic 0 is driven onto the LED). I have attached the reset to a sliding switch, and have tried uploading the configuration with the switch in either configuration.

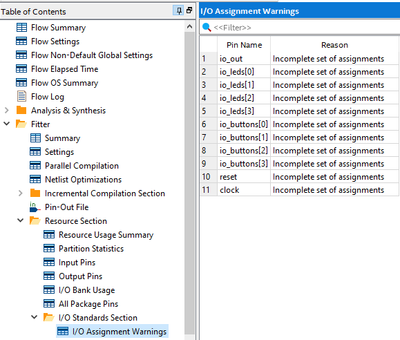

I have attached an image of my current pin mappings as well as the verilog code in question.

(As an aside: I'm also getting an error stating that all of my pin assignments are incomplete. I don't understand why this message is popping up. Any explanations?)

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You connected the LEDs to DIP switches (USER_DIPSW[3..0]), not the push buttons (USER_PB[2.0] on pins AN8, AA15, and AK13), so the LED's will be set based on the switch setting not the board pushbuttons. Your LED voltages are wrong as well. They should be 1.5 V according to the manual. The clock is OK on AG18 for 100 MHz or V28 for 50 MHz though again the I/O standard is wrong (should be LVDS). You can ignore the warnings for I/O because that just means you have to fill in each and every I/O assignment for each pin.

Also, this is a very strange way to code a counter/register since you check the reset signal twice in the same always block. Here's some better code (I didn't test the code but this makes more sense):

reg [31:0] cntReg;

wire max = cntReg == 32'hee6b280;

wire [31:0] cntNext = cntReg + 32'h1;

reg regOut;

wire inverse = ~regOut;

assign io_out = regOut;

assign io_leds = io_buttons;

always @(posedge clock) begin

if (reset) begin

cntReg <= 32'h0;

regOut <= 1'h1;

end

else begin

if (max) begin

cntReg <= 32'h0;

regOut <= inverse;

end

cntReg <= cntNext;

end

end

endmodule

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page