- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am currently developing a filtering project using MAX 10 FPGA and Quartus Prime 17.1 development software。The filter is prepared to use the fir ii IP core to filter out frequencies above 500Hz.

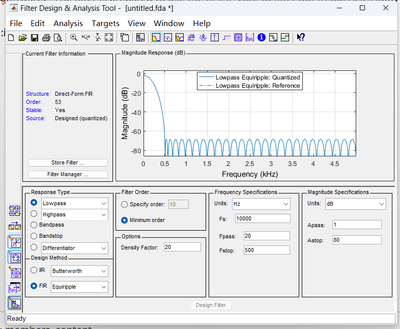

This is my setting in Matlab:

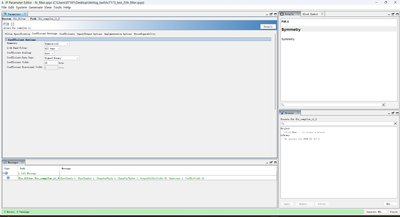

This is my setting in the fir ii IP core:

I have checked all the settings, but the output of the simulation is very strange. Here is my simulation result:

This problem has been bothering me for a long time and I haven't found a solution. I hope the community can give me some answers

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

It seems you are having clock rate and sampling rate mismatch issues. CLK RATE is 50MHz and Sampling rate is 10ksps and my understanding is that you are capturing or simulating FIR output at 50MHz can you capture the samples and do the PWELCH in MATLAB at 10ksps and check are you getting 25Hz?

Also, to confirm mismatch issue can you please try to make CLK and sampling rate same and then do the simulation.

And if still does not resolve the issue please share your project. I will look into it.

Thank you,

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I guess that ast_sink_valid isn't correctly driven by the sample rate. As suggested show your code, at least filter instantiation.

Filter output options can be optimized, you have unused MS bits and insignificant LS bits. If coefficients are copied 1:1 from Matlab design, 3 MS bits can stripped in "saturation" mode to achieve unity gain, output would be usually truncated to 16 - 24 bits by stripping respective LS bits.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As we do not receive any response from you on the previous answer that we have provided. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

Thank you,

Kshitij Goel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page