- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello there,

I'm trying to run a simulation in Questa using a testbench file that utilizes runtime arguments. The testbench file will check these runtime arguments and use the value to control the type of simulation that will be run. I originally used this testbench for a command-line simulator where you could pass the extra arguments into the simulation command. However, I'm not exactly sure where those runtime arguments would come into the Questa simulation flow, or whether or not it's even possible. Is this something I'm able to do?

- Tags:

- Questa

- simulation

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Are you referring to something like this?

https://www.theartofverification.com/plusargs-in-systemverilog/

Best Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

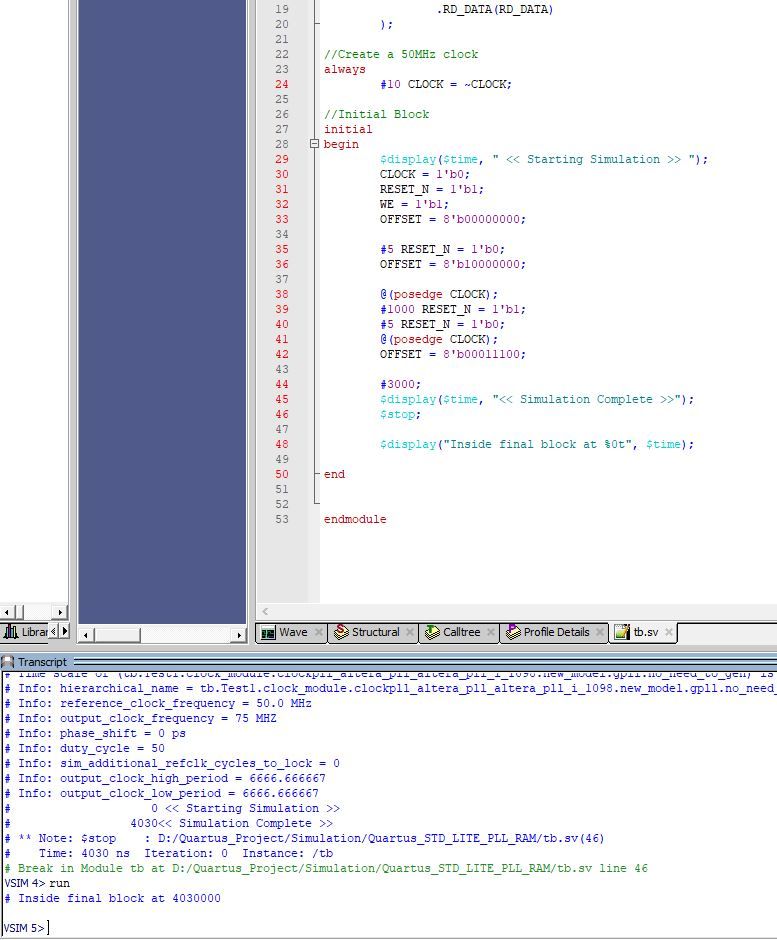

Yes exactly. I was able to fix the issue by adding the runtime argument to the elab_debug command in my .do file:

elab_debug +RUNTIME_ARG

Another issue I'm having is with the final procedure in my testbench. I believe the final procedure is supposed to run at the end of the simulation after $finish is called in the initial block. But when running the simulation I don't see any of the $display statements from the final block shown in the transcript window. Should I make a separate post for this or can you answer here? Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You're correct that the final procedure in a testbench typically runs after the $finish statement in the initial block.

If you're not seeing the $display statements from the final block in the transcript window, there could be a few reasons.

Ensure that the Final block executed in zero times, which implies it can't have any delay, wait, or non-blocking assignments.

See if the final block is instantiated at the correct level of hierarchy in testbench. If it's nested within another block that finished early, it might not get a chance to execute.

Perhaps you can try out a working example to see if it works. If it works, you will need to review the testbench.

Example tb: https://vlsiverify.com/system-verilog/systemverilog-final-block/#google_vignette

Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Richard,

I've tried the example testbench from this link and I think I may have realized what the problem may be. It also did not work with the example but I believe it's because of what the $finish statement does in Questa.

For my own testbench and the example testbench, when it reaches the $finish statement, Questa will show a prompt asking "Are you sure you want to finish?". If you choose "Yes", the Questa application will close. Because of this, I always chose "No". Choosing "No" will allow the waveform to display and all the $display statements in the initial block will show in the Transcript window, but I think because I choose "No", the $finish command does not get registered, so the final block will not run.

So now my question is: why does Questa close when choosing "Yes" for this prompt, and how do I make it so that doesn't happen?

Best,

Allen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello there,

Are you still able to help with this issue?

Allen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry for the delay due to Chinese New Year.

I noticed that when use $finish, it ends the simulation outright. Conversely, $stop halts the simulation and transitions to interactive mode. So, technically, you can utilize $stop.

Nonetheless, even if you use $finish, Questa typically prompts whether you want to end. Opting for 'no' allows you to stay within the simulation, while selecting 'yes' will exit Questa.

https://stackoverflow.com/questions/2395132/whats-the-difference-between-stop-and-finish-in-verilog

At this point, I suggest consulting Siemens, as they are experts in using the Questa* Core software. (Questa*-Intel® FPGA Starter software editions are a version of Siemens EDA Questa* Core software targeted for Intel FPGA devices.)

Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Richard,

Thanks for the reply. I have tried to use $stop in my simulation, and it does pause the simulation without the "Are you sure you want to finish?" prompt, but the issue is that using $stop will not trigger the final procedure to run. Only using $finish will do that according to what I've read. In the screenshot you attached, you're not using a final procedure block, just putting more statements after the $stop command in the initial block.

I think that will be a good workaround for now, but it would just require an extra "run" command that needs to be typed in the transcript window after the simulation stops. I'll try to see if Siemens has a fix for this.

Thanks so much for your help.

Best,

Allen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My apologies that I don't have the best answer to your inquiry. This will require consulting Siemens for a better solution.

If you are able to obtain the answer, please help by sharing the solution here for others who might have the same question.

Now, I will transition this thread to community support. If you have any further questions or concerns, please don't hesitate to reach out.

Thank you and have a great day!

Regards,

Richard Tan

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page