- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

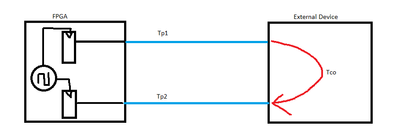

I am using a Cyclone V device and have another external device that is supposed to take input from the FPGA and return a value to the FPGA where it is then latched. I have attached an diagram of the scenario below. What is the correct timing constraint to apply to properly constrain this?

I was thinking about set_input_delay and set_output_delay, but I'm not sure how to extrapolate the required values since the input delay relies on the FPGA's internal propagation delay of the output and vice versa. That can't happen because those internal propagation delays are not known until fitting.

Thank you

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So the external device is just combinatorial logic or does it also have input and output registers?

If it's just logic (not clocked), you could probably use set_max_delay and set_min_delay between the output and input ports to define all the external delay. Just add up the trace delays and tco (is it called tco in the device's spec but not clocked? Hmm.) to come up with values.

Or are you saying that the FPGA clocks the external device which then sends a value back to the FPGA? In that case, that's a feedback design, so you'd need to define the output clock from the FPGA as a generated clock, set the output port as a false path so it is not analyzed as a data output, and use set_input_delay on the input, referencing the output clock and setting max/min values based on the total trace and tco delay through the external device.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It is combinatorial logic.

When using set_max_delay and set_min_delay between the ports, there isn't an internal path between the two. How does the max_delay then apply for that? I called it Tco because I was looking at Intel Design examples and all of the internal device delays were Tco so I decided to call it the same just to be consistent, doesn't really make sense in this case if you know what CO stands for.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

[Edited]

I think use set_max_delay and set_min_delay between the output and input ports means like below (tsu, th, tco(max/min) are external device value):

Input Ports:

set_max_delay -from [get_ports {<input>}] [board delay(max)+<Tco_Requirement>]

set_min_delay -from [get_ports {< input >}] [board delay(min)+<MinTco_Requirement>]

Output Ports:

set_max_delay -to [get_ports {<output>}] [board delay(max)+<Tsu_Requirement>]

set_min_delay -to [get_ports {<output>}] [board delay(min)-<Th_Requirement>]

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think you may ignore the above as combinatorial logic don't have tsu and th. Sorry for confusing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For the synchronous I/O external device:

Check this virtual class link https://learning.intel.com/Developer/learn/courses/841/intelr-quartusr-prime-pro-software-timing-analysis-part-4-io-interfaces/lessons/1506:99/intelr-quartusr-prime-pro-software-timing-analysis-part-4-io-interfaces (page 18-29) and this link https://community.intel.com/t5/FPGA-Wiki/Timing-Constraints/ta-p/735562 on set_input_delay and set_output_delay.

For the constraints, just need to know the board delay(max/min), board clock skew(max/min) and external device's tsu, th, tco(max/min) will do. The FPGA's internal propagation delay will be handled and calculated by the tool itself.

Thanks,

Best Regards,

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Its not a synchronous IO Device, its combinatorial. Perhaps the usage of Tco in the external device is confusing. That is just the combinatorial propagation delay.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I was thinking using -from the output and -to the input in the same constraint. Just add up the loop delays (trace + "tco") and use as the value. You don't need to know/use a th or tsu for this.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Does the program apply the constraint in the way I want it to? Will the timing analyzer "create" a timing path between those two ports that allows the program to use both internal delays during an individual calculation?

For example, Let's say there is

- A generated internal output delay of 2ns

- A total external propagation delay of 3ns

- And a generated internal input delay of 1ns

Would the program be able to recognize that it needs to add the 1ns from the input to the output's max_delay calculation for a total of 6ns?

Thank you for all the information so far,

Tucker Zischka

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The internal delays would be set up based on the external delay. That's how set_input_delay and set_output_delay work. If you define the external delay with set_max_delay and set_min_delay, it should work the same way.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I added the following constraints.

set_max_delay -from [get_ports output_port] -to [get_ports input_port] 10.368

set_max_delay -from [get_ports output_port] -to [get_ports input_port] 0

After rerunning compilation and checking timing, Delays and the Clock Skews for the Registers immediately before the output ports and after the input ports are as follows:

- Clock Delay for the output register is 8.263ns

- The data delay from the output register to the output port is 8.302ns

- The maximum external propagation delay is 10.368ns

- Clock Delay for the input register is 7.773ns

- The data delay from the input port to the input register is 9.817ns

- The clock is running at 120MHz = 8.333ns

The question is, what kind of analysis is being performed on this path now? The ports are currently unconstrained so it is not doing a synchronous analysis.

Doing the math here, there is a negative slack of:

Data Required Time - Data Arrival Time = Slack

(8.333+7.773+9.817) - (8.263+8.302+10.368 ) = -1.01ns

It's not doing that analysis nor reporting the "violation". I expect it to report the violation because the maximum external delay would cause the data to arrive after the latch clock edge.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Why do you have two set_max_delay constraints with different values? The second one should be set_min_delay.

Your data required calculation is incorrect. It should be (8.333 + 7.773 - tsu), whatever the setup timing requirement of the input register is.

Your data arrival time calculation is missing the data input delay. It should be (8.263 + 8.302 + 10.368 + 9.817) but that obviously makes things worse. The input and output delays and clock delays are way too big. The input and output registers are getting placed very far from the I/O to have data delays over 8 and 9.

Are you using a PLL? Have you tried using the fast I/O register assignments to use the registers located directly in the I/O cells?

And you're saying the tool still says these I/O are unconstrained?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Typed the command twice. The first is the correct one.

Yes, thank you for the corrections. It is even worse than what I originally typed out.

The implementation details are not of importance since I am working on those still. The tool should have certainly caught the timing issues at this point considering such abysmal timing.

The tool does say these I/O are unconstrained.

I'm not sure the set_max_delay command did what I wanted it to do considering it didn't catch this. Any Insight?

set_max_delay -from [get_ports output_port] -to [get_ports input_port] 10.368

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page