- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using Agilex 7 (AGFB022R25A2I3V). I wish to use the internal bridges to write to and read from DDR4.

My idea is like this,...

Build a internal connections using Platform Designer in Quartus Prime Pro. Then generate the Avalon-mm addresses of the DDR4.

At the Linux driver / application code, we write C program to write to and read from the specific address of the DDR4.

Do you know where I can find such sample project? I have been trying to search for months yet still can't find it. I have gone through a lot of intel documents and video clips. Yet still they can't help.

I am still not successful in implementing my requirement.

Could you please help?

Regards

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Is that an SoC device? Are you talking about the dedicated EMIF for the HPS in an SoC or just a standard EMIF connected to the FPGA? Lots of info available.

EMIF IP user guide: https://www.intel.com/content/www/us/en/docs/programmable/683216/23-2-2-7-1/about-the-external-memory-interfaces.html

Example design user guide: https://www.intel.com/content/www/us/en/docs/programmable/683162/23-1-2-7-0/about-the-external-memory-interfaces.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell,

I have gone through and followed the documents you recommended. Still I still get errors when I tried to generate using Platform Desginer.

I followed the document to make an EMIF IP and integrate it into the GHRD built from https://www.rocketboards.org/foswiki/Projects/SettingUpAndUsingBridgesOnAgilex

I still got the error, ...

HPS_OSC_CLK input is required to drive the main PLL. But the pin has not been specified in the HPS I/O selection.

Error: clk_100: "Board" (board) "default" is out of range: "Unknown", "Agilex Development Kit", "Arria 10 SoC Development Kit", "Stratix 10 SoC Development Kit", "Unknown"

I don't know how to solve these errors. Could you please guide me?

By the way, what's the difference between

1. External Memory Interfaces for HPS Intel Agilex FPGA IP and

2. External Memory Interfaces Intel Agilex FPGA IP

?

I can see that #1 has hps_emif conduit while #2 doesn't have. But if you use Hard Processor System Intel Agilex FPGA IP, it has hps_emif. If you use #1, you can connect with the hps_emif together. If you use #2, the hps_emif will have no connection.

If you follow the attached document, it's guiding you to make #2.

For read/write with DDR4, which one should be used?

After the above is built, at the Linux side, how can I write to and read from the DDR4 addresses?

For this requirement, I can see that there are 2 parts. One at the FPGA and one at the SoC Linux. Do you have the sample of this kind of project?

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell,

Is there any answer for this?

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

There is an example for interfacing with DDR4 with the example below:

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi Jingyang,

Thanks for coming back.

But can we use the Arria 10 or Cyclone V method on Agilex 7? Their architectures are different.

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I tried to run compilation at the Quartus Prime Pro 22.1.

A lot of pins needs to be removed in the ghrd_agilex_top.vhd, such as (pls look at the commented off ones)

port (

-- wd_reset_reset_n : out std_logic; -- reset_n

-- agilex_hps_f2h_stm_hw_events_stm_hwevents : in std_logic_vector(43 downto 0) := (others => 'X'); -- stm_hwevents

-- agilex_hps_h2f_cs_ntrst : in std_logic := 'X'; -- ntrst

-- agilex_hps_h2f_cs_tck : in std_logic := 'X'; -- tck

-- agilex_hps_h2f_cs_tdi : in std_logic := 'X'; -- tdi

-- agilex_hps_h2f_cs_tdo : out std_logic; -- tdo

-- agilex_hps_h2f_cs_tdoen : out std_logic; -- tdoen

-- agilex_hps_h2f_cs_tms : in std_logic := 'X'; -- tms

-- hps_io_EMAC0_TX_CLK : out std_logic; -- EMAC0_TX_CLK

-- hps_io_EMAC0_TXD0 : out std_logic; -- EMAC0_TXD0

-- hps_io_EMAC0_TXD1 : out std_logic; -- EMAC0_TXD1

-- hps_io_EMAC0_TXD2 : out std_logic; -- EMAC0_TXD2

-- hps_io_EMAC0_TXD3 : out std_logic; -- EMAC0_TXD3

-- hps_io_EMAC0_RX_CTL : in std_logic := 'X'; -- EMAC0_RX_CTL

-- hps_io_EMAC0_TX_CTL : out std_logic; -- EMAC0_TX_CTL

-- hps_io_EMAC0_RX_CLK : in std_logic := 'X'; -- EMAC0_RX_CLK

-- hps_io_EMAC0_RXD0 : in std_logic := 'X'; -- EMAC0_RXD0

-- hps_io_EMAC0_RXD1 : in std_logic := 'X'; -- EMAC0_RXD1

-- hps_io_EMAC0_RXD2 : in std_logic := 'X'; -- EMAC0_RXD2

-- hps_io_EMAC0_RXD3 : in std_logic := 'X'; -- EMAC0_RXD3

-- hps_io_EMAC0_MDIO : inout std_logic := 'X'; -- EMAC0_MDIO

-- hps_io_EMAC0_MDC : out std_logic; -- EMAC0_MDC

-- hps_io_SDMMC_CMD : inout std_logic := 'X'; -- SDMMC_CMD

-- hps_io_SDMMC_D0 : inout std_logic := 'X'; -- SDMMC_D0

-- hps_io_SDMMC_D1 : inout std_logic := 'X'; -- SDMMC_D1

-- hps_io_SDMMC_D2 : inout std_logic := 'X'; -- SDMMC_D2

-- hps_io_SDMMC_D3 : inout std_logic := 'X'; -- SDMMC_D3

-- hps_io_SDMMC_CCLK : out std_logic; -- SDMMC_CCLK

-- hps_io_UART0_RX : in std_logic := 'X'; -- UART0_RX

-- hps_io_UART0_TX : out std_logic; -- UART0_TX

-- hps_io_UART1_RX : in std_logic := 'X'; -- UART1_RX

-- hps_io_UART1_TX : out std_logic; -- UART1_TX

-- hps_io_gpio1_io0 : inout std_logic := 'X'; -- gpio1_io0

-- hps_io_gpio1_io1 : inout std_logic := 'X'; -- gpio1_io1

-- hps_io_gpio1_io4 : inout std_logic := 'X'; -- gpio1_io4

-- hps_io_gpio1_io5 : inout std_logic := 'X'; -- gpio1_io5

-- hps_io_jtag_tck : in std_logic := 'X'; -- jtag_tck

-- hps_io_jtag_tms : in std_logic := 'X'; -- jtag_tms

-- hps_io_jtag_tdo : out std_logic; -- jtag_tdo

-- hps_io_jtag_tdi : in std_logic := 'X'; -- jtag_tdi

-- hps_io_hps_osc_clk : in std_logic := 'X'; -- hps_osc_clk

-- hps_io_gpio1_io19 : inout std_logic := 'X'; -- gpio1_io19

-- hps_io_gpio1_io20 : inout std_logic := 'X'; -- gpio1_io20

-- hps_io_gpio1_io21 : inout std_logic := 'X'; -- gpio1_io21

-- h2f_reset_reset : out std_logic; -- reset

-- f2h_irq1_irq : in std_logic_vector(31 downto 0) := (others => 'X'); -- irq

clk_100_clk : in std_logic := 'X'; -- clk

-- emif_hps_pll_ref_clk_clk : in std_logic := 'X'; -- clk

-- emif_hps_oct_oct_rzqin : in std_logic := 'X'; -- oct_rzqin

-- emif_hps_mem_mem_ck : out std_logic_vector(0 downto 0); -- mem_ck

-- emif_hps_mem_mem_ck_n : out std_logic_vector(0 downto 0); -- mem_ck_n

-- emif_hps_mem_mem_a : out std_logic_vector(16 downto 0); -- mem_a

-- emif_hps_mem_mem_act_n : out std_logic_vector(0 downto 0); -- mem_act_n

-- emif_hps_mem_mem_ba : out std_logic_vector(1 downto 0); -- mem_ba

-- emif_hps_mem_mem_bg : out std_logic_vector(0 downto 0); -- mem_bg

-- emif_hps_mem_mem_cke : out std_logic_vector(0 downto 0); -- mem_cke

-- emif_hps_mem_mem_cs_n : out std_logic_vector(0 downto 0); -- mem_cs_n

-- emif_hps_mem_mem_odt : out std_logic_vector(0 downto 0); -- mem_odt

-- emif_hps_mem_mem_reset_n : out std_logic_vector(0 downto 0); -- mem_reset_n

-- emif_hps_mem_mem_par : out std_logic_vector(0 downto 0); -- mem_par

-- emif_hps_mem_mem_alert_n : in std_logic_vector(0 downto 0) := (others => 'X'); -- mem_alert_n

-- emif_hps_mem_mem_dqs : inout std_logic_vector(8 downto 0) := (others => 'X'); -- mem_dqs

-- emif_hps_mem_mem_dqs_n : inout std_logic_vector(8 downto 0) := (others => 'X'); -- mem_dqs_n

-- emif_hps_mem_mem_dq : inout std_logic_vector(71 downto 0) := (others => 'X'); -- mem_dq

-- emif_hps_mem_mem_dbi_n : inout std_logic_vector(8 downto 0) := (others => 'X'); -- mem_dbi_n

button_pio_external_connection_export : in std_logic_vector(3 downto 0) := (others => 'X'); -- export

dipsw_pio_external_connection_export : in std_logic_vector(3 downto 0) := (others => 'X'); -- export

led_pio_external_connection_in_port : in std_logic_vector(2 downto 0) := (others => 'X'); -- in_port

led_pio_external_connection_out_port : out std_logic_vector(2 downto 0); -- out_port

reset_reset_n : in std_logic := 'X'; -- reset_n

ninit_done_ninit_done : out std_logic -- ninit_done

);

end component qsys_top;

port map (

-- wd_reset_reset_n => open, -- wd_reset.reset_n

-- agilex_hps_f2h_stm_hw_events_stm_hwevents => stm_hw_events, -- agilex_hps_f2h_stm_hw_events.stm_hwevents

-- agilex_hps_h2f_cs_ntrst => '1', -- agilex_hps_h2f_cs.ntrst

-- agilex_hps_h2f_cs_tck => '1', -- .tck

-- agilex_hps_h2f_cs_tdi => '1', -- .tdi

-- agilex_hps_h2f_cs_tdo => open, -- .tdo

-- agilex_hps_h2f_cs_tdoen => open, -- .tdoen

-- agilex_hps_h2f_cs_tms => '1', -- .tms

-- hps_io_EMAC0_TX_CLK => hps_emac0_TX_CLK, -- hps_io.EMAC0_TX_CLK

-- hps_io_EMAC0_TXD0 => hps_emac0_TXD0, -- .EMAC0_TXD0

-- hps_io_EMAC0_TXD1 => hps_emac0_TXD1, -- .EMAC0_TXD1

-- hps_io_EMAC0_TXD2 => hps_emac0_TXD2, -- .EMAC0_TXD2

-- hps_io_EMAC0_TXD3 => hps_emac0_TXD3, -- .EMAC0_TXD3

-- hps_io_EMAC0_RX_CTL => hps_emac0_RX_CTL, -- .EMAC0_RX_CTL

-- hps_io_EMAC0_TX_CTL => hps_emac0_TX_CTL, -- .EMAC0_TX_CTL

-- hps_io_EMAC0_RX_CLK => hps_emac0_RX_CLK, -- .EMAC0_RX_CLK

-- hps_io_EMAC0_RXD0 => hps_emac0_RXD0, -- .EMAC0_RXD0

-- hps_io_EMAC0_RXD1 => hps_emac0_RXD1, -- .EMAC0_RXD1

-- hps_io_EMAC0_RXD2 => hps_emac0_RXD2, -- .EMAC0_RXD2

-- hps_io_EMAC0_RXD3 => hps_emac0_RXD3, -- .EMAC0_RXD3

-- hps_io_EMAC0_MDIO => hps_emac0_MDIO, -- .EMAC0_MDIO

-- hps_io_EMAC0_MDC => hps_emac0_MDC, -- .EMAC0_MDC

-- hps_io_SDMMC_CMD => hps_sdmmc_CMD, -- .SDMMC_CMD

-- hps_io_SDMMC_D0 => hps_sdmmc_D0, -- .SDMMC_D0

-- hps_io_SDMMC_D1 => hps_sdmmc_D1, -- .SDMMC_D1

-- hps_io_SDMMC_D2 => hps_sdmmc_D2, -- .SDMMC_D2

-- hps_io_SDMMC_D3 => hps_sdmmc_D3, -- .SDMMC_D3

-- hps_io_SDMMC_CCLK => hps_sdmmc_CCLK, -- .SDMMC_CCLK

-- hps_io_UART0_RX => hps_uart0_RX, -- .UART0_RX

-- hps_io_UART0_TX => hps_uart0_TX, -- .UART0_TX

-- hps_io_UART1_RX => hps_uart1_RX, -- .UART1_RX

-- hps_io_UART1_TX => hps_uart1_TX, -- .UART1_TX

-- hps_io_gpio1_io0 => hps_gpio1_io0, -- .gpio1_io0

-- hps_io_gpio1_io1 => hps_gpio1_io1, -- .gpio1_io1

-- hps_io_gpio1_io4 => hps_gpio1_io4, -- .gpio1_io4

-- hps_io_gpio1_io5 => hps_gpio1_io5, -- .gpio1_io5

-- hps_io_jtag_tck => hps_jtag_tck, -- .jtag_tck

-- hps_io_jtag_tms => hps_jtag_tms, -- .jtag_tms

-- hps_io_jtag_tdo => hps_jtag_tdo, -- .jtag_tdo

-- hps_io_jtag_tdi => hps_jtag_tdi, -- .jtag_tdi

-- hps_io_hps_osc_clk => hps_ref_clk, -- .hps_osc_clk

-- hps_io_gpio1_io19 => hps_gpio1_io19, -- .gpio1_io19

-- hps_io_gpio1_io20 => hps_gpio1_io20, -- .gpio1_io20

-- hps_io_gpio1_io21 => hps_gpio1_io21, -- .gpio1_io21

-- h2f_reset_reset => h2f_reset, -- h2f_reset.reset

-- f2h_irq1_irq => f2h_irq1_irq, -- f2h_irq1.irq

clk_100_clk => system_clk_100_internal, -- clk_100.clk

-- emif_hps_pll_ref_clk_clk => emif_hps_pll_ref_clk, -- emif_hps_pll_ref_clk.clk

-- emif_hps_oct_oct_rzqin => emif_hps_oct_oct_rzqin, -- emif_hps_oct.oct_rzqin

-- emif_hps_mem_mem_ck => emif_hps_mem_mem_ck, -- emif_hps_mem.mem_ck

-- emif_hps_mem_mem_ck_n => emif_hps_mem_mem_ck_n, -- .mem_ck_n

-- emif_hps_mem_mem_a => emif_hps_mem_mem_a, -- .mem_a

-- emif_hps_mem_mem_act_n => emif_hps_mem_mem_act_n, -- .mem_act_n

-- emif_hps_mem_mem_ba => emif_hps_mem_mem_ba, -- .mem_ba

-- emif_hps_mem_mem_bg => emif_hps_mem_mem_bg, -- .mem_bg

-- emif_hps_mem_mem_cke => emif_hps_mem_mem_cke, -- .mem_cke

-- emif_hps_mem_mem_cs_n => emif_hps_mem_mem_cs_n, -- .mem_cs_n

-- emif_hps_mem_mem_odt => emif_hps_mem_mem_odt, -- .mem_odt

-- emif_hps_mem_mem_reset_n => emif_hps_mem_mem_reset_n, -- .mem_reset_n

-- emif_hps_mem_mem_par => emif_hps_mem_mem_par, -- .mem_par

-- emif_hps_mem_mem_alert_n => emif_hps_mem_mem_alert_n, -- .mem_alert_n

-- emif_hps_mem_mem_dqs => emif_hps_mem_mem_dqs, -- .mem_dqs

-- emif_hps_mem_mem_dqs_n => emif_hps_mem_mem_dqs_n, -- .mem_dqs_n

-- emif_hps_mem_mem_dq => emif_hps_mem_mem_dq, -- .mem_dq

-- emif_hps_mem_mem_dbi_n => emif_hps_mem_mem_dbi_n, -- .mem_dbi_n

button_pio_external_connection_export => fpga_debounced_buttons, -- button_pio_external_connection.export

dipsw_pio_external_connection_export => fpga_dipsw_pio, -- dipsw_pio_external_connection.export

led_pio_external_connection_in_port => fpga_led_internal, -- led_pio_external_connection.in_port

led_pio_external_connection_out_port => fpga_led_internal, -- .out_port

reset_reset_n => (system_reset_n AND FPGA_TESTIO1), -- reset.reset_n

ninit_done_ninit_done => ninit_done -- ninit_done.ninit_done

);

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can some experts please help on the sample Quartus project DDR4 with Agilex 7?

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Are you using a dev kit or a custom board? If it's a dev kit, you can select the board when creating the Quartus project and then generate the example design from the EMIF IP parameter editor. A GHRD project is for a particular device and dev kit, so if you are having issues with it, then you must not be using that dev kit. If you are not using a dev kit and this is your own custom board, you can (and should) still create an example design and use that for testing. You would still need to set location assignments for the I/O, but you can use Interface Planner for that or follow the guidelines in the IP user guide to manually create the assignments. This is all shown in the training I linked you to.

FYI: Rzq is for the OCT (on-chip termination) calibration so that must be connected to an Rzq pin with a resistor attached. Again, all documented in the IP user guide.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell,

Thanks for coming back to me.

I have gone through the links you provided long before I decided to post my question here.

I am not sure. But if you think the links you provided is able to help, why not you try them and make a working project and load into the Agilex 7 board you have and see if you can read write on DDR4 through your Linux application program. Say we write 500MB of data to the DDR4 and read back. It has to go through the bridges you have created using the EMIF in the documents in the links you provided.

Could you please try that?

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I don't have the hardware for this. I'm going by my experience with the IP and tools and implementation of EMIF on other devices. And I run in Windows, not Linux. You still don't mention if this is a dev kit or your own custom board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell,

I am using the board designed based on a development kit.

To quote you...

"If it's a dev kit, you can select the board when creating the Quartus project and then generate the example design from the EMIF IP parameter editor."

"If you are not using a dev kit and this is your own custom board, you can (and should) still create an example design and use that for testing."

Whether or not it is dev kit, does it matter? Still we need to create example design, right?

Do the documents, that say creating example from the EMIF IP, work?

My thinking is that if the documents says it is working, there should be some sample project that can support and show it is working. Instead, we need to read all the documents and test it and to tell if the documents are valid, working theoretically. But I think, theoretically, it is working. Practically, something is missing, causing it doesn't work.

Am I right to say that?

Frankly, I have tried almost all documents and video clips, be it DDR4, EMIF, etc. Yet, none works... It is either failing at the generate part at the Platform Designer or at the compilation part at Quartus Prime Pro. In short, it all fails...

Sigh...I may have overlooked something. That's why I need some experts here to guide me.

The requirement here sounds simple, Bringing up the internal bridges in Agilex 7 so that at the Linux application side, it can read from and write to the DDR4.

But when implementing it, it's not that simple.

It's quite funny when I asked people around me. They either know the FPGA part or the SoC part. None knows both combination. Some suggested using UART or SPI to access to the DDR4. But it's slower. It doesn't make sense since the internal bridges are there. We need to bring up the internal bridges to access to the DDR4. It is faster, right? But how to bring up the internal bridges to achieve this?

I even thought of writing my own AXI4 signals to access to the DDR4. But there are 2 obstacles here.

One is how to write the AXI4 signals itself, for sure.

The second one is that even this can be achieved, at the Linux side, it will have problem accessing it since there is no memory-mapped addresses to access the DDR4, like the one generated by Avalon-mm.

Could someone please help?

Regards,

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Since this is a custom board, forget about the bridges and the HPS for now. You're taking on too much at once. If it was a dev kit, the GHRD would have been sufficient. That's why I said that it makes a difference what board you're using. Create an example design in the EMIF IP Parameter editor for your EMIF design. This creates an entire Quartus project including a traffic generator for testing. Use Interface Planner (or just the Pin Planner) to place the I/O appropriately for your board. That seems to be your biggest issue at this point, and the training and EMIF IP user guide goes into detail on how to do this.

Once you've got the EMIF working, you can then move on to adding the HPS into the mix since you will have all the I/O locations and EMIF parameters set correctly and you'll know they are working. Add it to the example design project created by the EMIF IP Parameter editor or create a new project and copy over all the settings and parameters.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell,

"Once you've got the EMIF working, you can then move on to adding the HPS into the mix since you will have all the I/O locations and EMIF parameters set correctly and you'll know they are working. Add it to the example design project created by the EMIF IP Parameter editor or create a new project and copy over all the settings and parameters."

I have tried this also. It fails at the generate step at the Platform Designer.

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What error(s) are you getting in Platform Designer when you try to generate? Or are you saying it fails when you are trying to create the example design? What version of Quartus?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It fails with this error message when I tried to generate

HPS_OSC_CLK input is required to drive the main PLL. But the pin has not been specified in the HPS I/O selection.

Sorry, it's actually a warning. It matters also, right?

I am using Quartus Prime Pro 22.1.0 Build 174 03/03/2022 SC Pro Edition.

Platform Designer 22.1 Build 174.

Do you want me to PM you my Quartus projects?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Like I said, you need to create an example design without the HPS and establish that your EMIF works. That warning means you are still trying to create the example design from the HPS EMIF IP, not the standalone EMIF IP.

But yes since it's just a warning, it's not an issue for now.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell,

OK.

I recreate again based on the attached document.

By the way. I asked the hardware engineer, he told me their design is based on Intel Agilex 7 FPGA F-series transceiver-SoC Development kit.

Does that ring any bell to you?

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

"Based on" or "is" an Agilex 7 F-series dev kit? If it actually is a dev kit, the GSRD is here and you can use that: https://www.rocketboards.org/foswiki/Documentation/AgilexSoCGSRD?erpm_id=7513446_ts1709705124515. If not, then you should continue getting the EMIF to work before incorporating the HPS.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell,

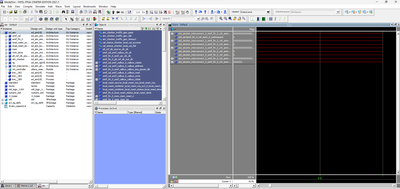

I have created the stand-alone EMIF based on the ug-ag-emideug-683162-773463.pdf document up to the modelsim part. What to see if it is working?

I attach the screenshot of the modelsim here.

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell,

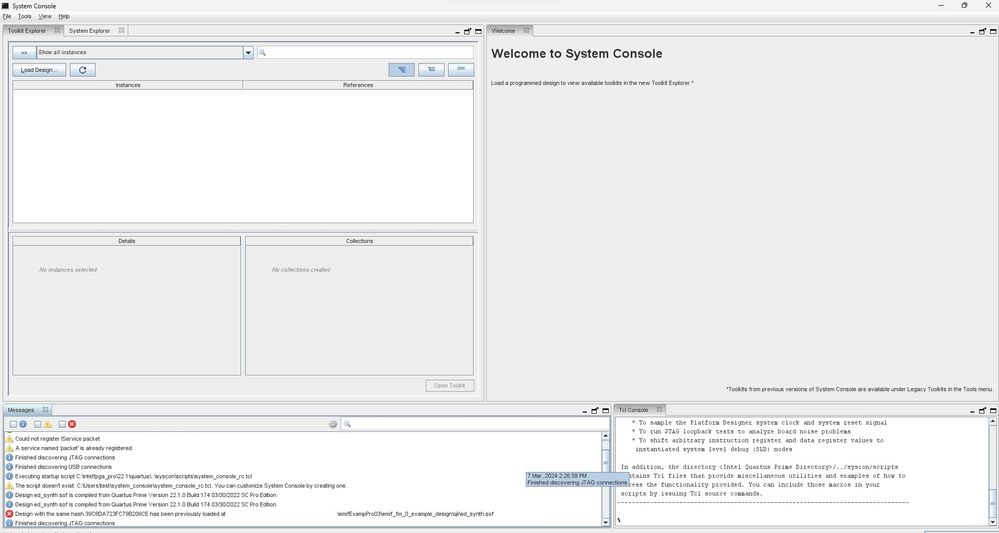

In the document "ug-ag-emideug-683162-773463.pdf", I am stuck at

2.11. Using the Design Example with the EMIF Debug Toolkit

5. Click Open Toolkit to open the main view of the EMIF Debug Toolkit.

I can't see any button by the name "Open Toolkit"

I loaded my ed_synth.sof by clicking on "Load Design" button. Then my System Console is empty, as shown below,...

We need this to check if EMIF is working before incorporating the HPS, right?

Regards

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page