- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi :

I use stratix10 series FPGA and PCIe AVMM DMA IP core,the system of the host computer is Linux,if I want to use multiple interrupts and software have different functions executed based on different interrupts, for example, printing "I received Interrupt 1" upon receiving Interrupt 1 and printing "I received Interrupt 2" upon receiving Interrupt 2, how can I achieve this?

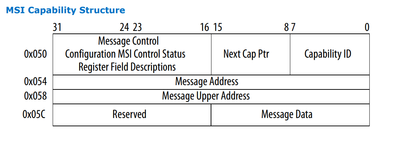

Based on my understanding of the user guide, the software should first configure the MSI or MSI-x capability. If I want to initiate an MSI interrupt, I only need to write data through the TXS interface. The address should be the Message Address configured by the software in the capability, and the data should be the Message Data configured by the software in the capability. How can 16-bit Message Data represent 32 different interrupts?

If anyone has ever used a PCIe IP core, could you briefly describe the process of using MSI/MSI-X interrupts, from software initialization to data interaction between FPGA and software?

- Tags:

- PCIe

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @allen18,

Thanks for reaching out.

Please allow me some time to investigate your issue. I’ll follow up with my findings.

Thank you for your patience.

Best Regards,

VenTing_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @allen18,

The software/driver implementation is out of my area of expertise, I’m happy to assist with any hardware-related aspects of the question.

There are two types of interrupts: legacy interrupt, and MSI and MSI-X interrupt.

MSI Interrupt:

Yes, MSI interrupt can be performed via the TXS interface. To trigger MSI interrupt, the Application can perform single DWORD memory writes, to be created by one of the AVMM slave interfaces. The Application can cause an MSI to be sent by the non-bursting Avalon-MM TX slave by performing a memory write to the non-bursting Avalon-MM TX slave. After the host receives an MSI it can service the interrupt based on the application defined interrupt service routine.

Besides, as many as 16 individual input interrupt signals are available but not 32 interrupt signals. You may find the rxm_irq_i [<m>:0], where <m> < 16 signal in Table 39 of the user guide given.

a. These signals connect interrupts to the AVMM interface. They are only available for the AVMM when the CRA port is enabled.

b. MSI interrupt is rising edge triggered. The hard IP core converts this event to an MSI interrupt and sends it to the Root Port.

c. The host reads the Interrupt Status register to retrieve the interrupt vector.

d. Host software services the interrupt and notifies the target upon completion.

e. The software must ensure that all interrupt sources are cleared for each MSI message received.

f. Note that, these signals are not available when the IP core is operating in DMA mode (i.e. when the Enable AVMM DMA option in the Avalon-MM Settings tab of the GUI is set to On)

The above findings are based on the below user guide: https://www.intel.com/content/www/us/en/docs/programmable/683667/23-1/introduction.html

You may also visit this article to learn more about the PCIe interrupts: https://community.intel.com/t5/FPGA-Wiki/Handling-PCIe-Interrupts/ta-p/736032

I hope these address your questions well.

Thanks.

Best Regards,

VenTing_Intel

p/s: If any answers from the community or Intel support are helpful, please feel free to mark them as solutions, give them kudos, and rate the survey 4/5.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @allen18,

May I know if there are any updates from your end regarding this forum case?

I look forward to your response which will allow us to proceed to the next step.

Thanks.

Best Regards,

VenTing_Intel

p/s: If any answers from the community or Intel support are helpful, please feel free to mark them as solutions, give them kudos, and rate the survey 4/5.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @allen18,

I wish to follow up with you on this forum case.

I hope to hear from you soon so that we can move forward to the next step.

Thanks.

Best Regards,

VenTing_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @allen18,

As we have not received any response from you on the previous reply that we have provided, I shall set this case to close pending. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you.

After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

If you feel your support experience was less than a 9 or 10, please allow me to correct it before closing, or please let me know the cause so that I may improve your future support experience.

Thanks.

Best Regards,

VenTing_Intel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page